Exzellenzcluster Cognitive Interaction Technology Kognitronik und Sensorik Prof. Dr.-Ing. U. Rückert

## Dynamically Reconfigurable Hardware for Embedded Control Systems

zur Erlangung des akademischen Grades eines

## DOKTOR-INGENIEUR (Dr.-Ing.)

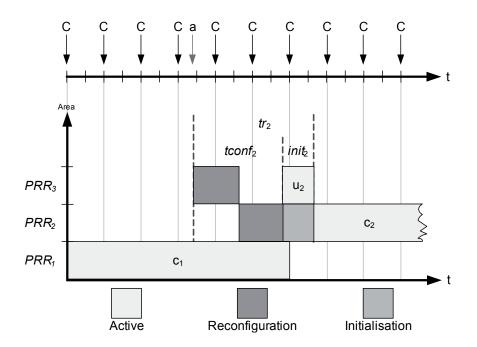

der Technischen Fakultät der Universität Bielefeld

genehmigte Dissertation

von

## M.Sc. Carlos Vladimir Paiz Gatica

Referent:Prof. Dr.-Ing. Ulrich RückertKorreferent:Prof. Dr.-Ing. Joachim Böcker

Tag der mündlichen Prüfung: 21. Dezember 2011

Paderborn / Januar 2012 DISS KS / 02

Para Araceli, mi compañera de vida, y Ernesto, nuestro fruto y esperanza.

#### Abstract

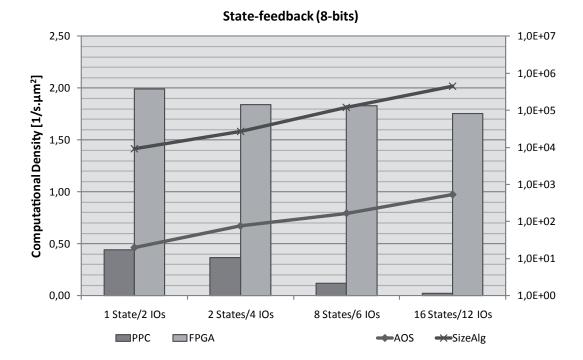

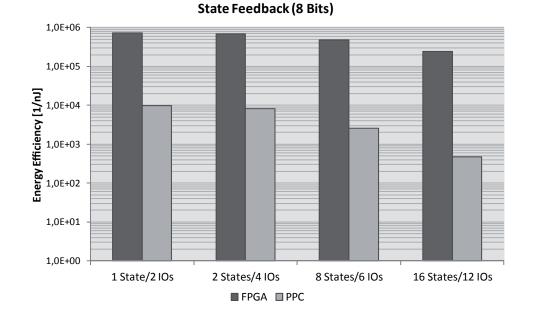

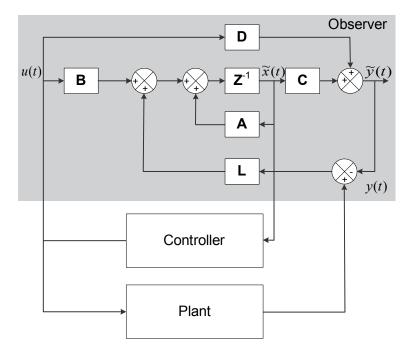

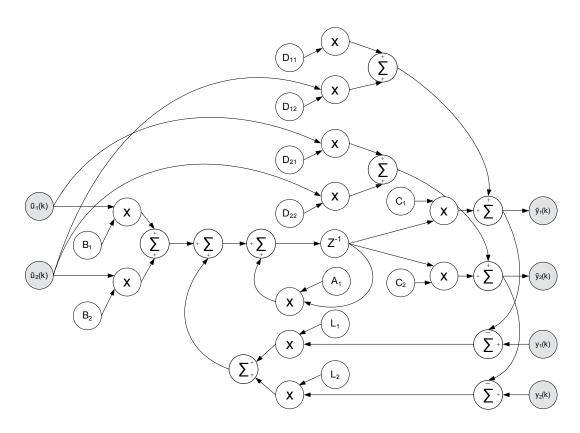

This thesis explores the use of dynamically reconfigurable hardware for the realisation of embedded control systems, using the most well-known example of this kind of technology: Field Programmable Gate Array (FPGA). The focus of the first part of the thesis is on assessing the resource utilisation of FPGA- and CPU-based realisations, relating the results to the algorithmic characteristics of the implemented controller, and the properties of both hardware and software architectures. Using a selected set of benchmarks, it is shown that an FPGA-based design achieves a higher computational density ( $C_{density}$ =throughput/area) and a higher energy efficiency ( $E_{efficiency}$ =throughput/power) than a CPU-based implementation. Furthermore, it is shown that when the average parallelism of the algorithm to be implemented increases when increasing the problem size (i.e., the amount of computations required for that algorithm), the gap between FPGA- and CPU-based realisations in terms of computational density increases, too.

The use of run-time hardware reconfiguration to achieve a more efficient resource utilisation than a static approach is investigated in the second part of this work. It is shown that control systems requiring structural and parametric adjustments during execution can benefit from run-time hardware reconfiguration. Application examples are presented showing that the proposed concepts are successfully realisable using current technologies, also for control applications having demanding time-constraints.

New design methodologies are required for embedded control systems using dynamically reconfigurable hardware, specially for those targeting run-time hardware reconfiguration. A Hardware-in-the-Loop design framework is presented in the third part of this work, which allows an early cycle-accurate verification of a design under test (DUT), using a simulated environment. In a second stage, the DUT can be monitored in real-time, and design parameters can be adjusted during operation, while using the target environment of the DUT. Several realisation examples show the efficacy of the proposed framework.

This thesis shows that dynamically reconfigurable hardware, particularly FPGA technology, is a suitable platform for demanding embedded control applications. Methods and tools presented in this thesis disclose the advantages of dynamically reconfigurable hardware, and represent a step towards taking full advantage of the possibilities offered by this technology, in the context of embedded control systems.

## Contents

| Al | ostra | ct       |                                                            | iii  |

|----|-------|----------|------------------------------------------------------------|------|

| 1  | Intr  | oductio  | on                                                         | 1    |

|    | 1.1   | Contri   | butions                                                    | 2    |

|    | 1.2   | Thesis   | Outline                                                    | 4    |

| 2  | Rea   | lisatior | n of Digital Control                                       | 7    |

|    | 2.1   | Digita   | l Control                                                  | . 7  |

|    |       | 2.1.1    | Software-Based Design                                      | 9    |

|    |       | 2.1.2    | ASIC-Based Design                                          | . 11 |

|    | 2.2   | Recon    | figurable Hardware                                         | 13   |

|    |       | 2.2.1    | Field Programmable Gate Array                              | 14   |

|    |       | 2.2.2    | General FPGA-Based Design Flow                             | 18   |

|    | 2.3   | Utilisa  | tion of Reconfigurable Hardware for Digital Control        | 19   |

|    |       | 2.3.1    | Application Spectrum                                       | 20   |

|    |       | 2.3.2    | Factors of the Technology Migration                        | 22   |

|    |       | 2.3.3    | Coupling of Reconfigurable Hardware and Software Architec- |      |

|    |       |          | tures                                                      | 30   |

|    |       | 2.3.4    | Run-Time Hardware Reconfiguration                          | 34   |

|    | 2.4   | Summ     | hary                                                       | 35   |

| 3  | Tec   | hnolog   | y Comparison of Reconfigurable Hardware and Software       | e    |

| -  |       | hitectu  |                                                            | 37   |

|    | 3.1   | Algori   | thmic Characterisation                                     | 38   |

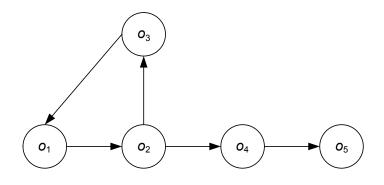

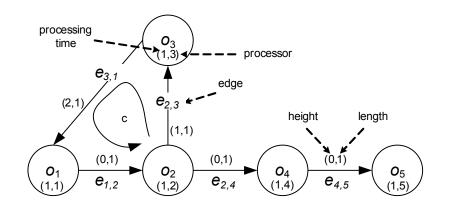

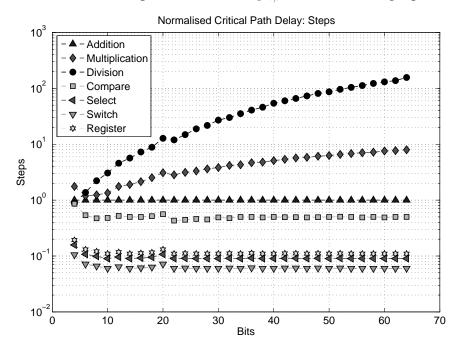

|    |       | 3.1.1    | Controller Representation: Cyclic Data Flow Graph          | 38   |

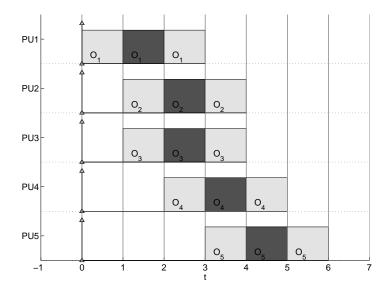

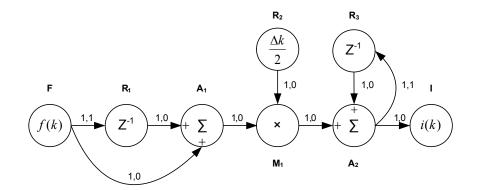

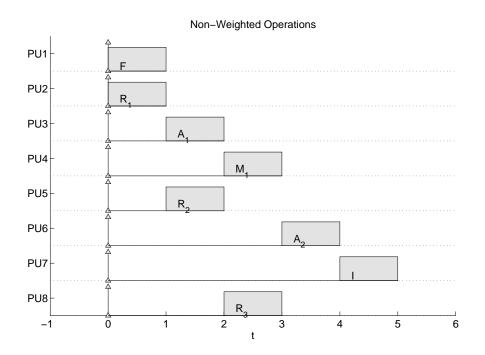

|    |       | 3.1.2    | Scheduling of a CDFG                                       | 39   |

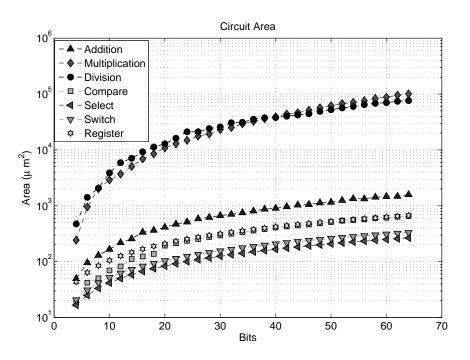

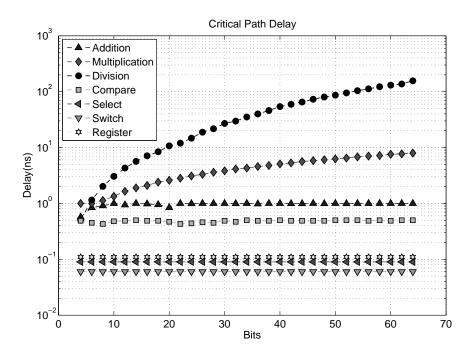

|    |       | 3.1.3    | Basic Operations Set: Selection and Weighting              | 41   |

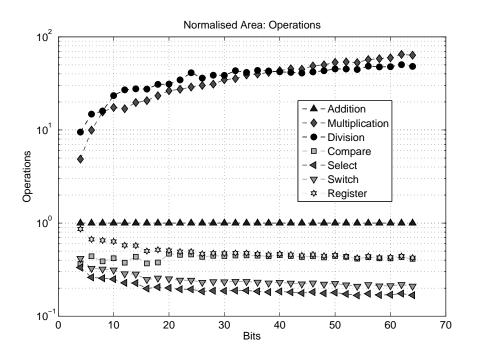

|    |       | 3.1.4    | Normalised Operations and Steps                            | 42   |

|    |       | 3.1.5    | Average Parallelism                                        | 48   |

|    | 3.2   | Resou    | rce Utilisation Assessment                                 | 50   |

|    |       | 3.2.1    | Computational Density                                      | 52   |

|    |       | 3.2.2    | Energy Efficiency                                          | 55   |

|    | 3.3   | Comp     | uting Architectures                                        | 56   |

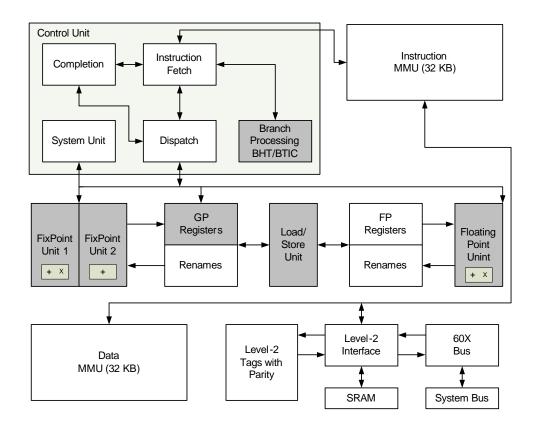

|    |       | 3.3.1    | PowerPC 750-G Processor                                    | 56   |

|   |     | 3.3.2   | FPGA Device                                         | 58    |

|---|-----|---------|-----------------------------------------------------|-------|

|   | 3.4 | Realisa | ation Flow                                          | 60    |

|   |     | 3.4.1   | Hardware Implementation-Flow                        | 60    |

|   |     | 3.4.2   | Software Implementation-Flow                        | 62    |

|   | 3.5 | Bench   | marks                                               | 63    |

|   |     | 3.5.1   | PID Controller                                      | 64    |

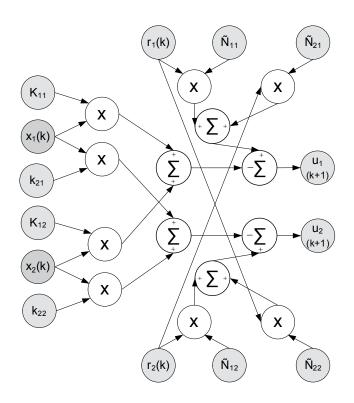

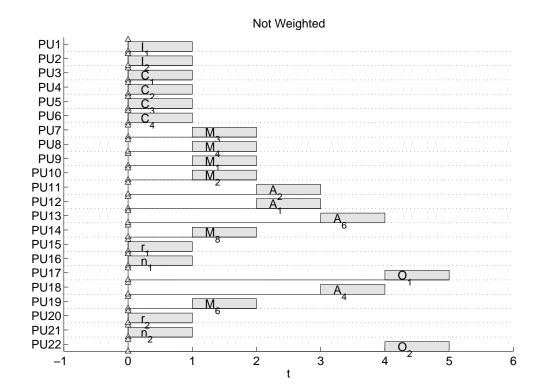

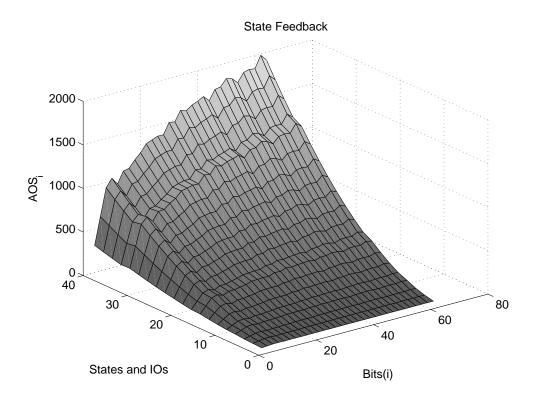

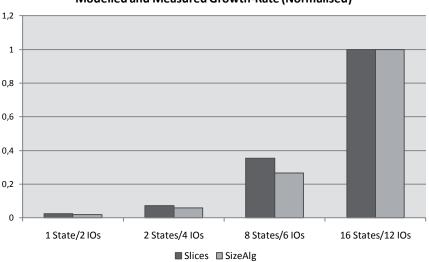

|   |     | 3.5.2   | State-Feedback Controller                           | 75    |

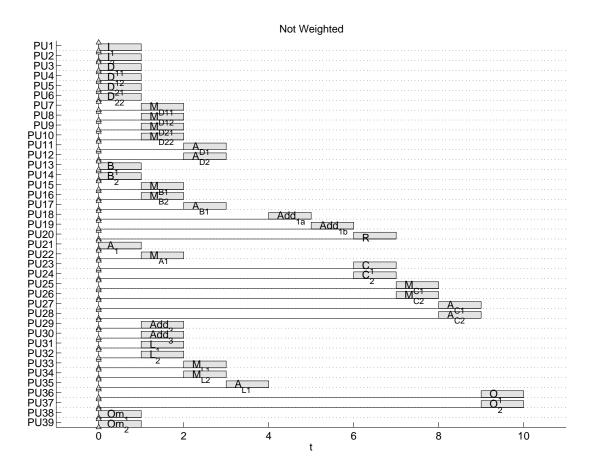

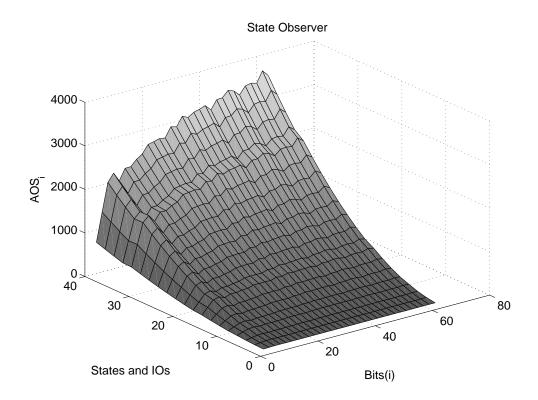

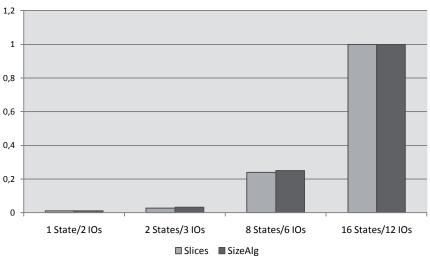

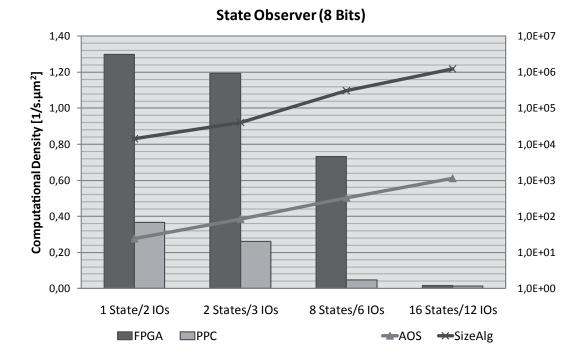

|   |     | 3.5.3   | State Observer                                      | 84    |

|   | 3.6 | Summ    | ary                                                 | 93    |

| 4 | Run | -Time   | Hardware Reconfiguration                            | 97    |

|   | 4.1 | Contro  | oller Adjustment                                    | 98    |

|   | 4.2 | Run-T   | Yame Hardware Reconfiguration                       | 100   |

|   |     | 4.2.1   | Configuration Granularity                           | 102   |

|   |     | 4.2.2   | Configuration Interface                             | 104   |

|   |     | 4.2.3   | Partial Reconfiguration Process                     | 105   |

|   |     | 4.2.4   | Partition and Placement Approaches                  | 108   |

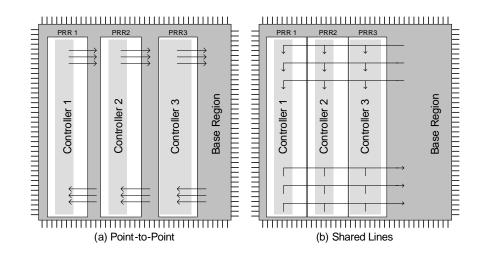

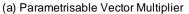

|   |     | 4.2.5   | Communication Infrastructure                        | 110   |

|   | 4.3 | Contro  | bl Adjustment Through Run-Time Reconfiguration      | . 111 |

|   |     | 4.3.1   | Structure Adaptation                                | . 111 |

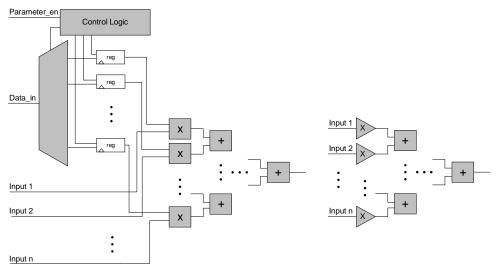

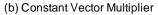

|   |     | 4.3.2   | Parameter Adaptation                                | 114   |

|   | 4.4 | Impler  | mentation Examples                                  | 116   |

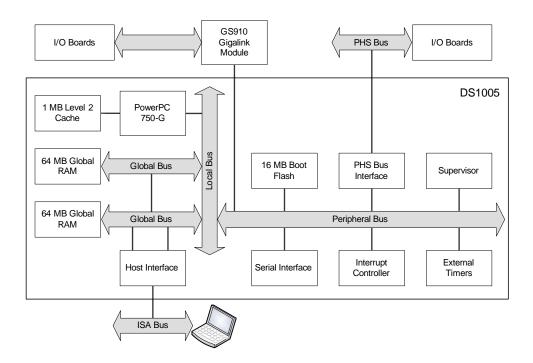

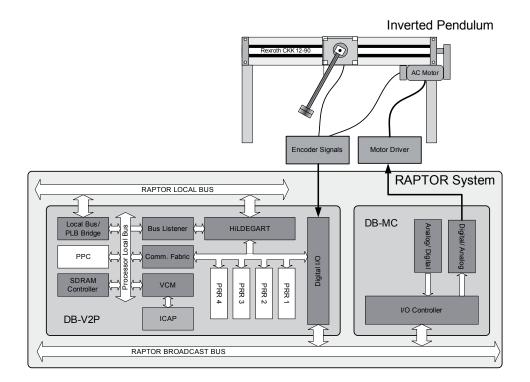

|   |     | 4.4.1   | The RAPTOR System                                   | . 117 |

|   |     | 4.4.2   | System Architecture                                 | 118   |

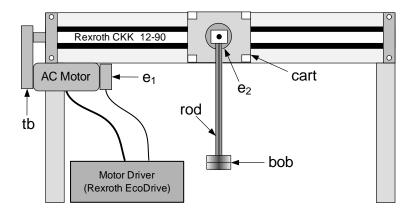

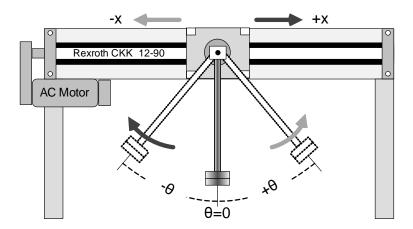

|   |     | 4.4.3   | Inverted Pendulum System                            | . 121 |

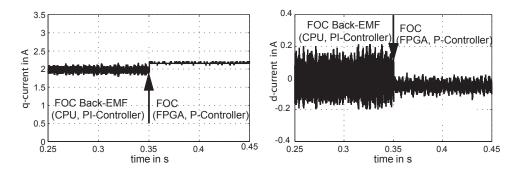

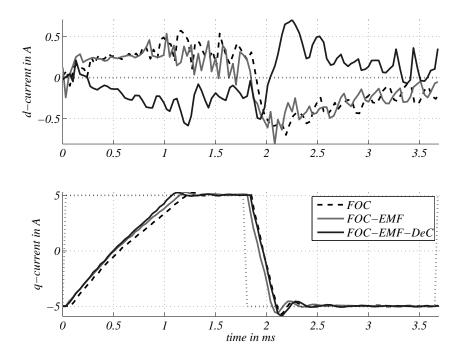

|   |     | 4.4.4   | Self-Optimising Motion Controller                   | 128   |

|   | 4.5 | Summ    | ary                                                 | 138   |

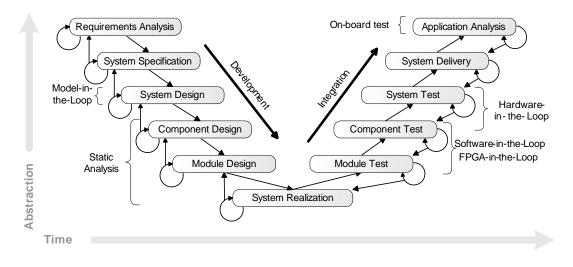

| 5 | Des | ign Vei | rification through Hardware-in-the-Loop Simulations | 141   |

|   | 5.1 |         | fication of Test-Systems                            | 142   |

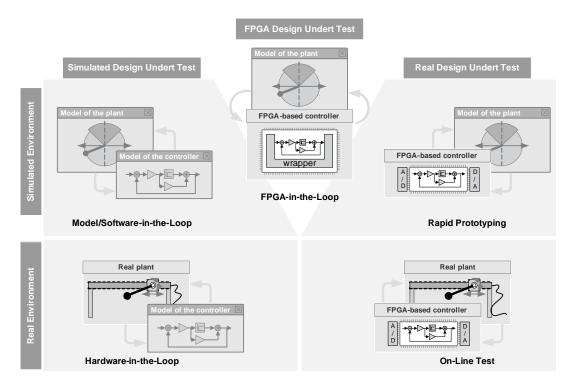

|   |     | 5.1.1   | Model- and Software-in-the-Loop                     | 142   |

|   |     | 5.1.2   | Rapid Prototyping                                   | 143   |

|   |     | 5.1.3   | Hardware-in-the-Loop Simulation                     | 143   |

|   |     | 5.1.4   | On-Line Test                                        | 143   |

|   |     | 5.1.5   | FPGA-in-the-Loop                                    | 144   |

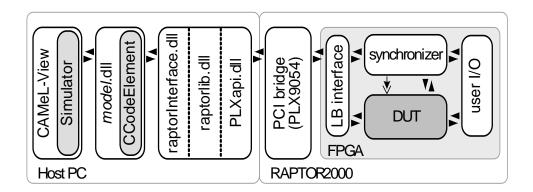

|   | 5.2 | HiLDI   | E: HiL Design Environment                           | 146   |

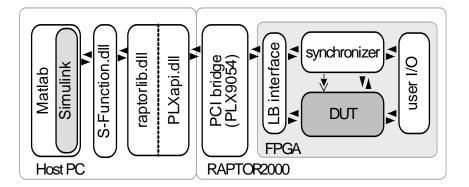

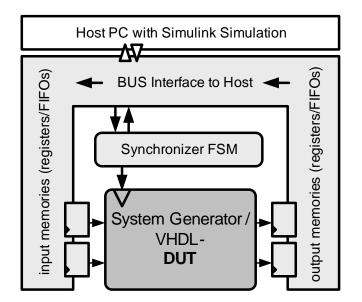

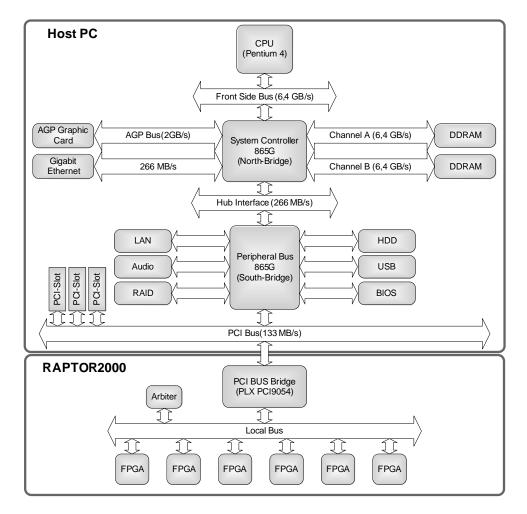

|   |     | 5.2.1   | Hardware Components                                 | . 147 |

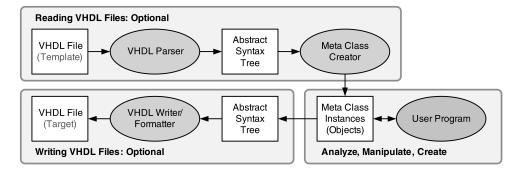

|   |     | 5.2.2   | Software Components                                 | 149   |

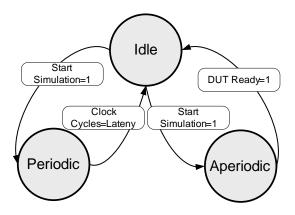

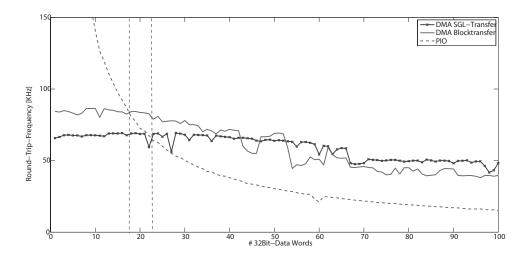

|   |     | 5.2.3   | Communication and Performance                       | . 151 |

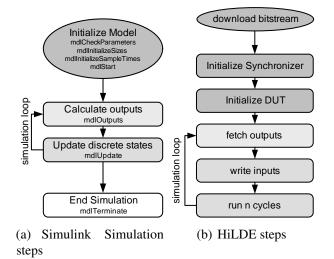

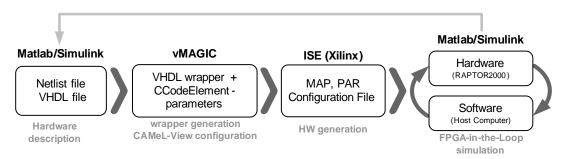

|   |     | 5.2.4   | HilDE Tool Flow                                     | 155   |

|   |     | 5.2.5   | Implementation Examples                             | 159   |

| 5.3    | HiLDEGART: HiL Design Environment for Guided Active Real-Time |       |  |

|--------|---------------------------------------------------------------|-------|--|

|        | Test                                                          | 166   |  |

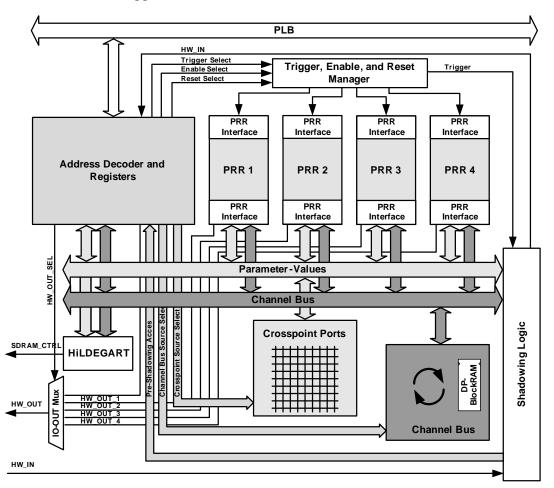

|        | 5.3.1 Hardware Components                                     | . 167 |  |

|        | 5.3.2 Software Components                                     | 168   |  |

|        | 5.3.3 HILDEGART Tool Flow                                     | 170   |  |

|        | 5.3.4 HiLDEGART Implementation Examples                       | . 171 |  |

| 5.4    | 4 Summary                                                     | 176   |  |

| 6 Su   | ummary and Outlook                                            | 177   |  |

| 6.1    | 1 Summary                                                     | . 177 |  |

| 6.2    | 2 Outlook                                                     | 180   |  |

| Autho  | or's Publications                                             | 183   |  |

| Biblio | ography                                                       | 187   |  |

| List o | of Figures                                                    | 205   |  |

| List o | of Tables                                                     | 211   |  |

| Gloss  | ary                                                           | 213   |  |

# **1** Introduction

Digital technology is constantly evolving in response to the ever-increasing computational requirements of modern society. A good example of this evolution is the so-called Moore's law, which says that the amount of transistors contained in a processor doubles every two years [Moo98]. This trend has been observed since the publication of the original paper in 1965, and will provably continue for some more decades. However, there are physical limitations (e.g., thermal noise [Kis02], transistor scaling limitations [Tho06], or power dissipation issues [Kis04]), which force us to look for other possibilities to increase performance. Furthermore, this exponential growth of the number of transistors in a processor does not necessarily results in exponential growth of CPU performance. One way to increase performance while keeping resource efficiency is to adapt the computer architecture to the application.

Digital Signal Processors (DSP) are a good example: the most common operation of applications in the domain of filtering or video processing is multiplication. Therefore, most of the current DSP architectures have at least one specialised multiply and accumulate (MAC) unit. Architectures for digital control have evolved similarly. Let us consider microcontrollers as an example. They have been used traditionally for motion control applications in both low-performance AC inverter drives and high-performance servo drives. This platform has evolved from very simple architectures to one-chip solutions, incorporating specialised DSP functions (e.g., MACs), Digital to Analog Converters, Analog to Digital Converters, Pulse Width Modulators, along with dedicated hardware for networked communication. This means that not only the level of specialisation, but also the level of architectural parallelism has been increased, by adding specialised processing units in response to application requirements.

In the last decade, the rise of more complex and more computation-intensive control schemes has motivated engineers and researchers to explore new architectures, or even new computing paradigms to reach the required performance. Reconfigurable Hardware (RH), specifically the most well-known architecture of this kind of technology, Field Programmable Gate Array (FPGA), has emerged as an alternative for demanding

applications, because of its high architectural parallelism, and the possibility to change the configuration of the device according to the application.

FPGAs are heterogeneous devices, constituted by programmable functional blocks and embedded application-specific hardware, such as embedded processors, memory, or multipliers, interconnected by a reconfigurable network. This allows for new ways to implement digital controllers, leaving the traditional CPU-based approach for a highly parallel realisation. However, can all kinds of control algorithms benefit from this technology for their realisation? Is an FPGA-based realisation faster, or less energy consuming than a CPU-based realisation? These questions motivate the first part of the present work.

It is well-known, that the feature of reconfigurability of SRAM-based FPGAs comes at the prices of a great amount of silicon resource dedicated to enable reconfiguration of logic elements (more than 80% of silicon resources [Fen06]). Are there ways to take advantage of resources dedicated for configuration when the device is in operation? For which kinds of control applications would such an approach be beneficial? The second part of the present work is inspired by these questions.

Furthermore, aspects of the design flow of digital controllers such as design verification and real-time monitoring, which are already standard for CPU-based design flows, are addressed in the last part of the present work. The main contributions of this thesis are summarised in the following section.

#### 1.1 Contributions

FPGAs offer a different approach to realise computations when compared to centralised architectures, such as general purpose processors. The architectural parallelism offered by FPGAs allows for spatial computation in contrast to the classical approach, in which a problem is first decomposed in single steps that are executed sequentially. The first contribution of this thesis is a quantitative comparison of software- and FPGA-based realisations, from a technological point of view. The main contributions are:

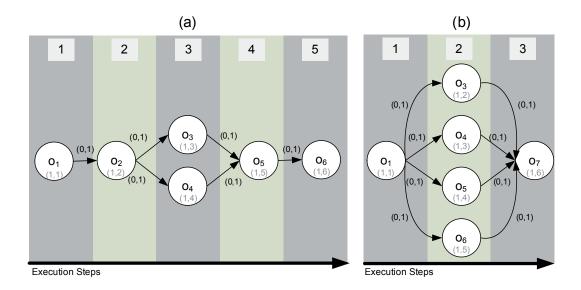

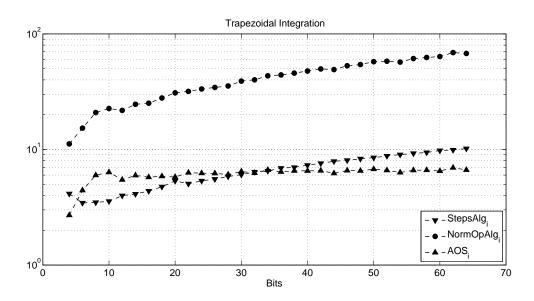

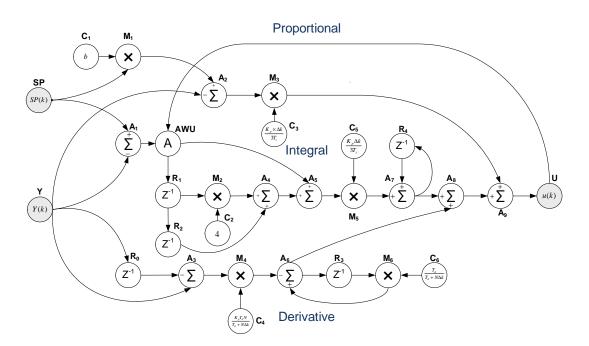

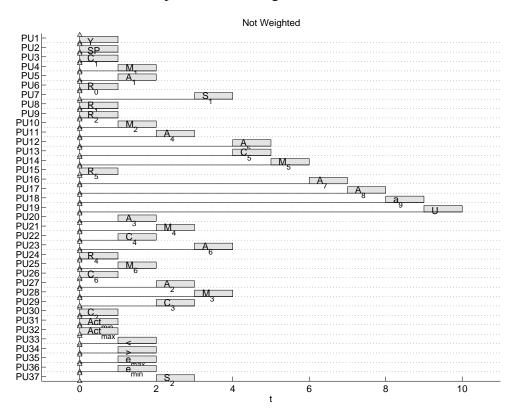

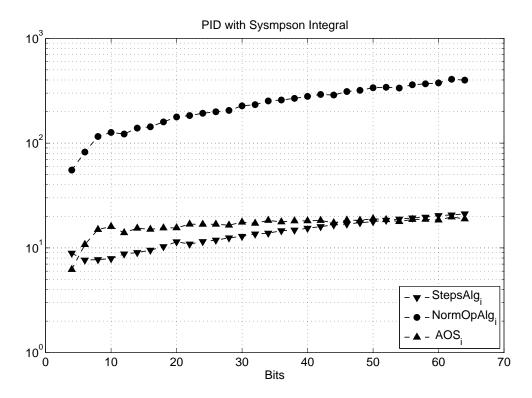

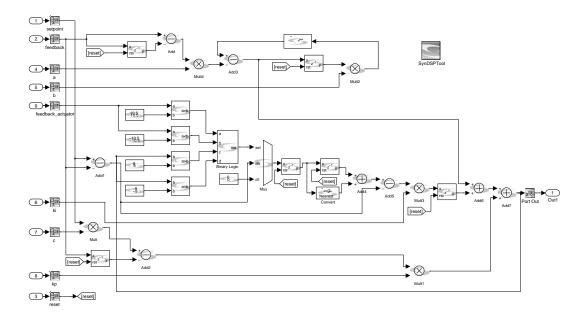

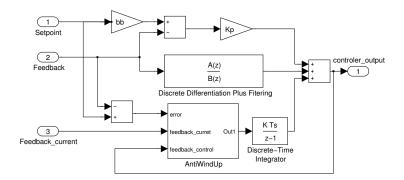

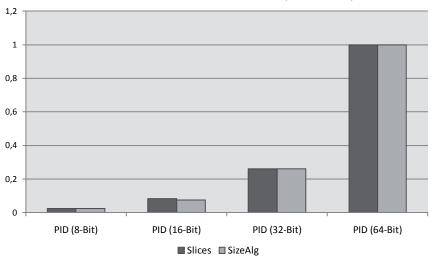

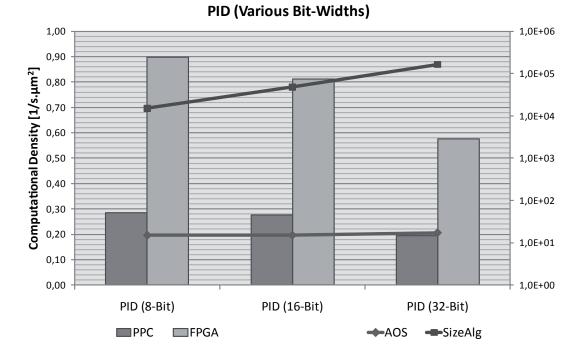

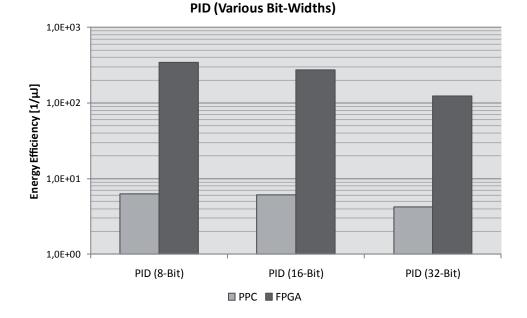

• A set of metrics is proposed to evaluate algorithmic characteristics of controllers. Particularly, the number of average operations per execution step (AOS) is used to measure average parallelism, which together with the size of the algorithm (SizeAlg) are used to characterise selected benchmarks. Furthermore, computational density ( $C_{density} = throughput/area$ ), and energy efficiency ( $E_{efficiency} = throughput/power$ ) are used to assess the resource utilisation of a hardware- and software-base realisation. Computational density and energy efficiency are metrics taken from literature and are adapted to the application field of control systems.

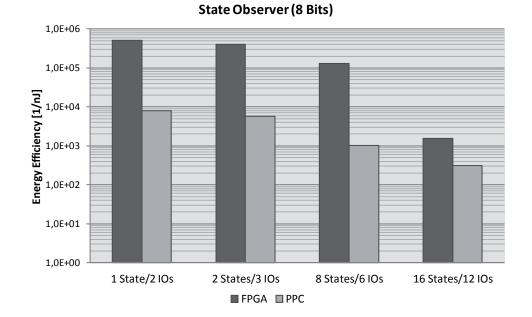

• Three representative control algorithm are chosen as benchmarks for this comparison: a PID controller, a state-feedback controller, and a full state observer. Based on the implementation results of these benchmarks, and on their algorithm characteristics, the advantage of realising controllers using FPGA technology are quantitatively demonstrated. It is shown that an FPGA implementation leads to a higher  $C_{density}$  and  $E_{efficiency}$ , which implies a more efficient use of resources. Presented implementation results show that an algorithm having an increasing problem size (i.e., *SizeAlg*) with constant average parallelism (i.e., *AOS*) derives in a reduction of the gap between FPGA- and CPU-based realisations, regarding achievable values of  $C_{density}$  and  $E_{efficiency}$ . On the contrary, when an algorithm has an increasing *AOS* when increasing *SizeAlg* the gap between FPGA- and CPU-based realisations increases, too.

Achievable performance decreases for controllers requiring more resources than those available in an FPGA device, because configurable logic has to be time-shared. This situation can be caused by having more resources occupied on an FPGA than those required at a given time. This is the case of control approaches requiring some kind of adjustment at run-time, because all possible configurations have to be loaded into the FPGA when the configuration of the device stays constant through the whole operation cycle (i.e., a static approach). To tackle this problem, the utilisation of run-time reconfiguration of FPGAs for control application is presented. The main contributions are summarised in the following paragraphs:

- It is shown that FPGA-based control systems requiring adjustments during operation can benefit from RTR. Two cases of adjustments are distinguished: structural and parametric changes.

- It is shown that the resource utilisation of a dynamic approach depends on the worst-case configuration of the system, whereas for a static implementation the resource utilisation depends on all required configurations. This can lead to a better resource utilisation for systems using run-time-reconfiguration, in contrast to a static approach (i.e., the configuration of the device does not change during operation).

- The problem of having a reaction time (i.e., reconfiguration times plus initialisation time) longer than the required control cycle is analysed and solutions are proposed.

- Implementation examples show that the proposed approach can be realised with current technology, also for demanding control applications.

An important part of the design of digital systems is verification. This thesis contributes in this field, by proposing a Hardware-in-the-Loop framework for FPGA-based designs. The main contributions are:

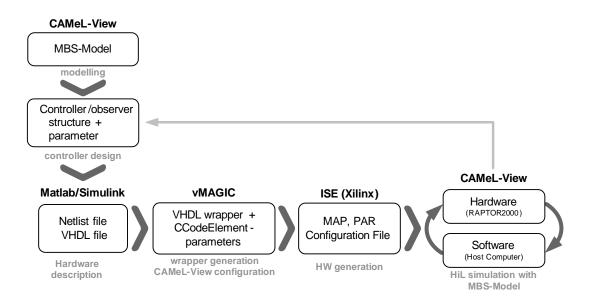

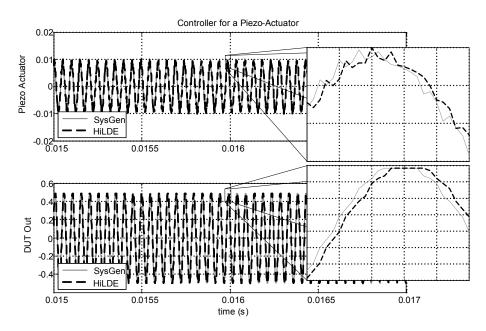

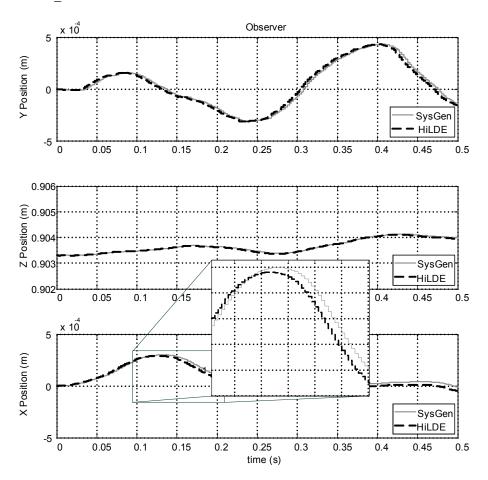

• A cycle-accurate FPGA-in-the-Loop simulation framework using well-known simulation tools such as Matlab/Simulink or CaMEL-View is presented. Hardware-

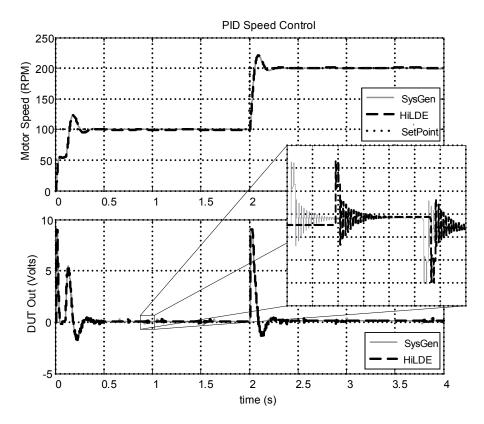

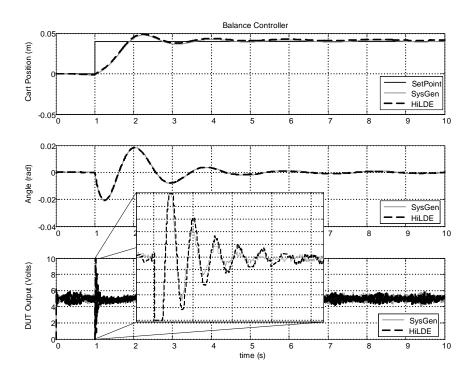

in-the-Loop Design Environment (HiLDE) allows the early verification of the design under test (DUT) using a simulated environment. Furthermore, it is shown that simulations are accelerated, shortening required design times. Several examples show the efficacy of HiLDE.

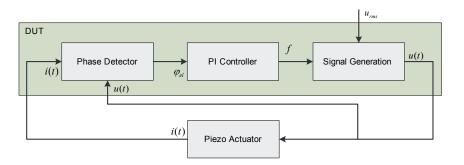

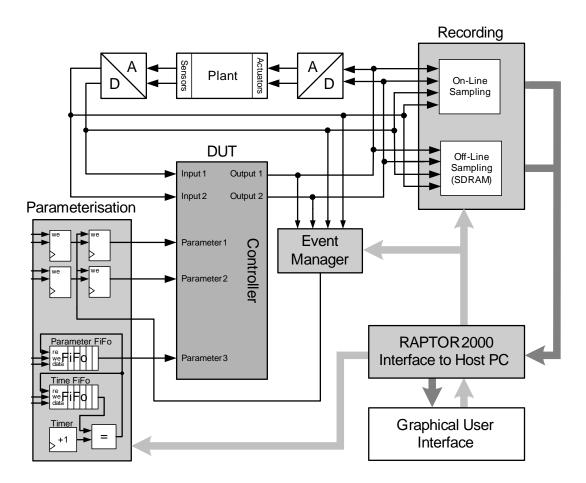

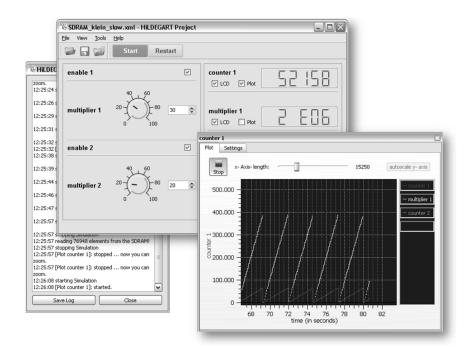

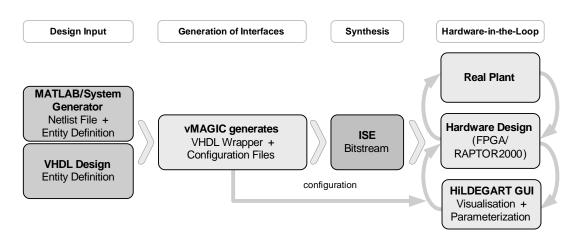

- A real-time test framework using the target environment of the DUT is introduced. The focus of this framework called HiLDEGART (HiLDE for Guided Active Real-Time Test) is on monitoring internal states and I/Os of a DUT while it is in operation, on adjusting design parameters, as well as on verifying timing issues. The advantages of using HiLDEGART are disclosed, using several prototypical implementations.

- A tool-flow is presented, which enables the automatic integration of a DUT to a HiL simulation (HiLDE or HiLDEGART), thus making the verification process easier and less error prone.

- Several realisation examples prove the efficacy of the proposed frameworks, also for applications requiring run-time reconfiguration.

These topics are addressed in the following chapters, as explained in the next section.

#### 1.2 Thesis Outline

Chapter 2 presents relevant background on digital control, showing the main differences between a software-, an ASIC-, and an FPGA-based design flow. The chapter offers a review of the state-of-the-art regarding the utilisation of reconfigurable hardware for control applications. It is shown that FPGAs are leaving their role as prototyping platforms to become the target architecture for demanding control applications. The reasons are examined and the research problems investigated in this work are motivated.

Chapter 3 explores the benefits and challenges of using FPGA-technology in contrast to a CPU-based realisation for embedded control applications. This chapter begins by introducing used metrics for algorithm characterisation and for resource utilisation assessment. Furthermore, the used computing architectures are presented in detail. The chapter continues by showing the design- and tool-flow used for the implementation of benchmarks. Implementation results and the corresponding analysis and discussion follows, and finally the main contributions are summarised.

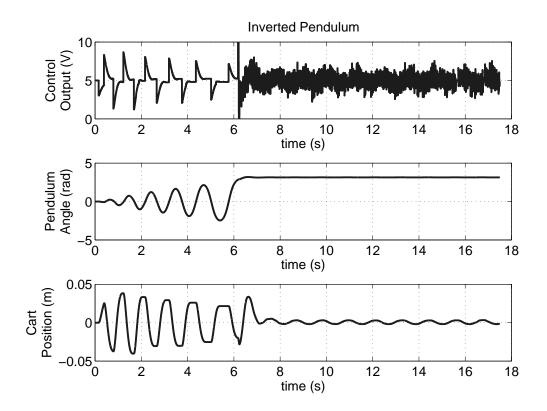

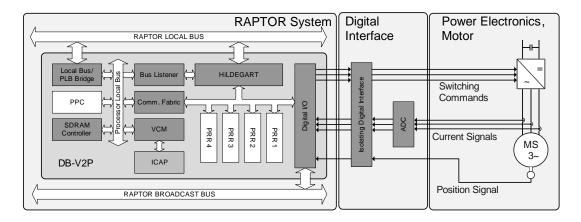

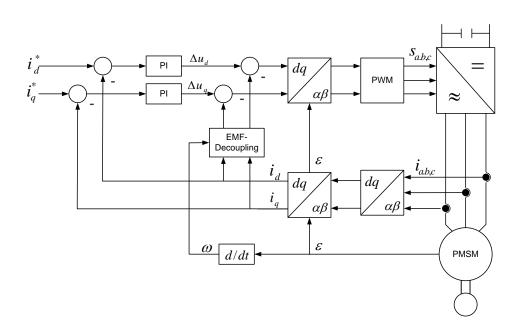

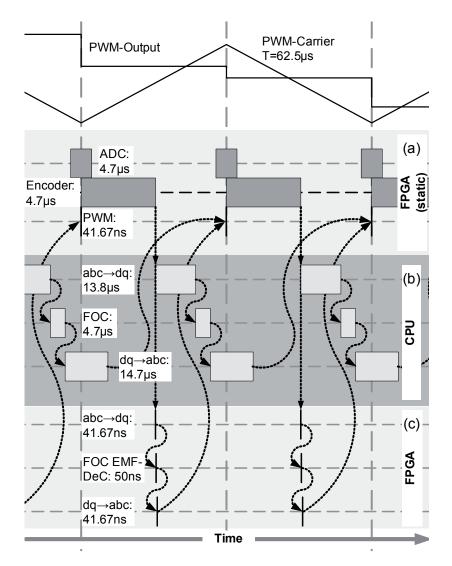

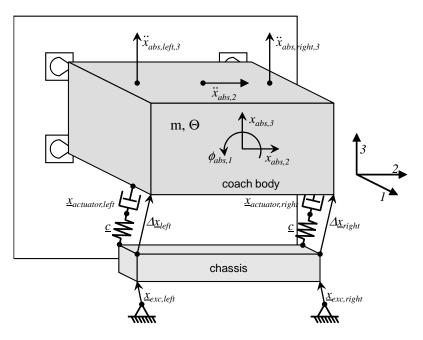

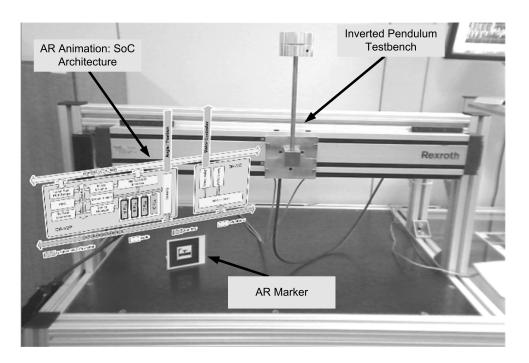

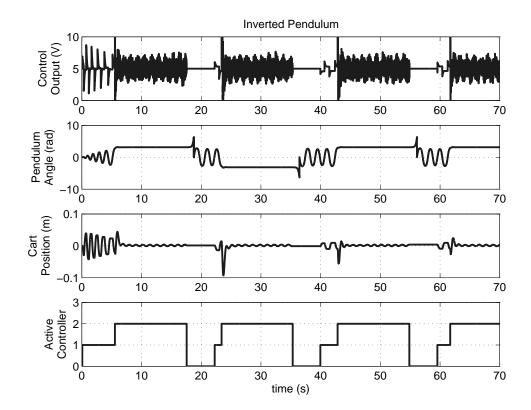

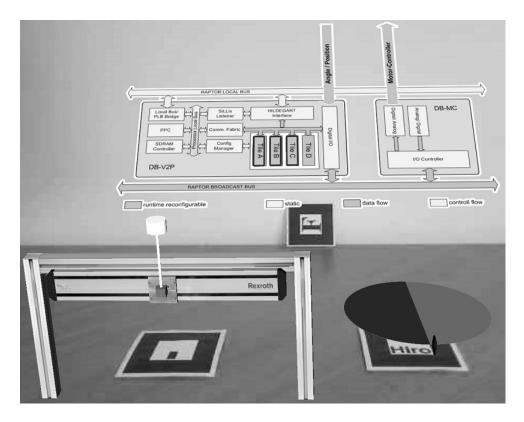

The use of run-time reconfiguration (RTR) for control applications is presented in chapter 4. The concept of RTR is explained, analysing different aspects of the design of systems using RTR. It is shown that FPGA-based control systems requiring some kind of adjustments during operation can benefit from RTR. Two cases of adjustments are distinguished: structural and parametric changes. For both cases RTR can be used to achieve a better resource utilisation, depending on the amount of structural variations, or the size of the algorithm requiring parametric changes. Two implementation examples are examined: a two-controller system for an inverted pendulum, and a self-optimizing motion controller. Prototypical realisations of the presented concepts show the advantage of this approach.

Chapter 5 introduces a Hardware-in-the-Loop design environment for FPGA-based controllers, which includes an off-line simulation framework (HiLDE) and an online monitoring tool (HiLDEGART). These frameworks support the design flow of FPGA-based controllers targeting run-time reconfiguration. Hardware and software components of both frameworks are presented, as well as a tool-flow which allows the automatic integration of the design under test. Several application examples are presented, showing the benefit of using HiLDE and HiLDEGART.

Finally, chapter 6 summarises the main results presented in previous chapters and offers conclusions, giving also an outlook based on analysis of collected experiences during this thesis work.

# **2** Realisation of Digital Control

This chapter introduces background concepts on digital control and reconfigurable hardware. The main contribution of the chapter is a literature review of the use of Field Programmable Gate Array (FPGA) technology for control applications. Based on this review, relevant research problems undertaken in the thesis are motivated. The chapter ends with a brief summary.

### 2.1 Digital Control

The aim of a controller is to influence the behaviour of a system, usually referred to as plant, by applying control signals in order to achieve a particular control objective. Control signals can be computed with or without direct information of the plant, which is known as open- and close-loop control, respectively. If direct information is gathered from the plant, control signals are usually a function of an error signal (e(k)); the difference between a desired value or set point, (s(k)) and a measured value (y(k)), cf. equation 2.1.

$$e(k) = s(k) - y(k)$$

(2.1)

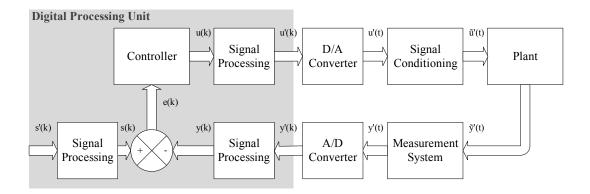

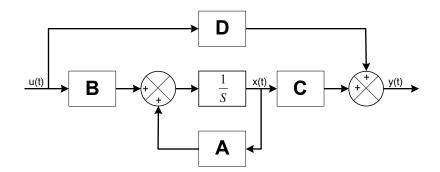

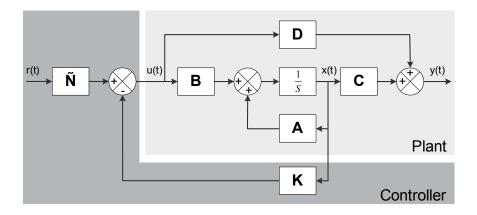

Digital control refers to the utilisation of signals discrete in value and time to control a plant. This process involves the utilisation of digital hardware (e.g., a processor) to compute the control effort. Figure 2.1 depicts a typical digital close-loop controller.

Feedback signals ( $\tilde{y}(t)$ , cf. figure 2.1) are typically measured by sensors, which convert a given form of energy, such as mechanical movement, heat, or light, into electrical signals. Sensor signals are ideally directly proportional to the measured property. These signals are usually conditioned (y'(t)), e.g., filtered and amplified, before they are digitalised (y(k)). The digitalisation implies three steps:

Figure 2.1: Block diagram of a typical digital control system

- 1. Sampling: involves the conversion of a signal continuous in time and amplitude into a signal discrete in time and continuous in amplitude. This process is done at regular intervals of time known as *sampling period*, which are considered to be constant.

- 2. Quantisation: is the conversion of the sampled signal into a discrete-time discrete-valued signal. A given signal sample is then represented by a finite binary string, whose length determines the quantization level, given by equation 2.2

$$QL = \frac{FSR}{2^n} \tag{2.2}$$

where FSR is the Full Signal Range (e.g., the maximum voltage level supported by the ADC), and n is the number of bits used for the quantization.

3. Coding: is the process, in which quantized samples are represented by a specific numbering format (e.g., fixed point, floating point).

Although these steps are presented as separated processes, they are generally done in a single chip, known as analog to digital converter (ADC). After data has been digitalised, it typically needs some kind of adjustment (y(k)), e.g., rescaling and filtering, which is a process done by the digital processing unit. Control signals (u(k))might require some processing (y'(k)) before they are converted to analog signals (y(t)). Correspondingly, analog outputs generally need some kind of conditioning, such as filtering or amplification,  $(\tilde{u}(t))$  before they can be applied to the plant.

Embedded digital controllers have quantifiable requirements, such as energy consumption, performance (hard real-time computation), and implementation costs. Therefore, the implementation of a controller based on an embedded device differs from a controller based on a general purpose computing platform, where those factors are not implicit.

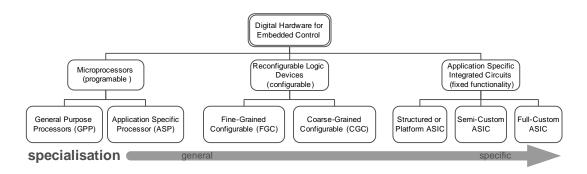

Figure 2.2: Digital hardware platforms to implement digital controllers classified according to the level of specialisation [Des06]

Traditionally, the target technologies for embedded digital controllers have been, on the one hand, software architectures varying in the level of specialisation, and on the other hand, application specific integrated circuit (ASIC). Recently, reconfigurable logic devices, particularly FPGA technology, have gained popularity as target platform. All these architectures differ in the level of specialisation to the application, as depicted in figure 2.2.

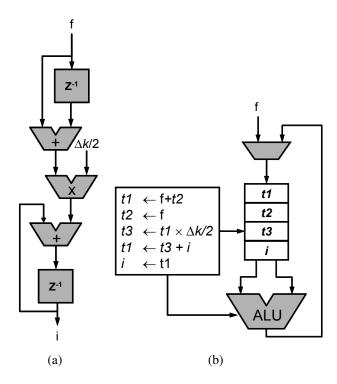

Microprocessors are based on a computation scheme, where a central processing element, e.g., an arithmetic logic unit (ALU), is used to sequentially process a set of instructions, which represent a temporally sequenced algorithm. These devices can compute any computable function, by changing their functionality every clock-cycle. On the contrary, when implementing a design in reconfigurable hardware, several processing elements can be used concurrently to compose the desired function, cf. figure 2.3. Reconfigurable hardware devices can compute any computation that fits the available resources (e.g., configurable elements), and are typically configured every operational epoch.

If the controller is implemented as an ASIC, several processing units can also be used concurrently (spatial implementation), but the device does not change its functionality after fabrication. The design flow of an embedded controller differs significantly depending on the target technology. These differences are pointed out in the following sections, where only the implementation using the target technology is considered.

#### 2.1.1 Software-Based Design

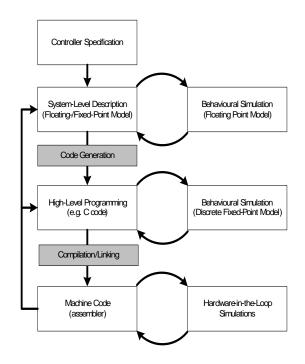

Software architectures have a common characteristic: little architectural parallelism (e.g., typically a single Arithmetic Logic Unit - ALU). Therefore, an algorithm to be computed has to be described as a list of instructions, which are executed sequentially. There are several approaches to implement controllers using embedded software

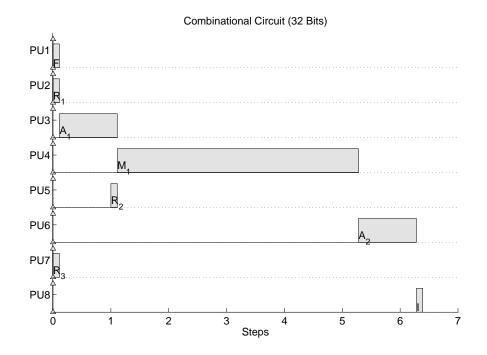

Figure 2.3: Spatial and temporal implementation of a proportional-integral controller (PI), using trapezoidal integration (sketch based on [DeH00])

architectures. However, typically the design starts by specifying the requirements (e.g., required sampling rate). In this stage a mathematical model of the plant is derived, together with a mathematical description of the controller. The use of high-abstraction level tools, such as Matlab/Simulink, or CaMEL-View is very common at this stage of the design flow. The controller is then simulated using either continuous-time floating-or fixed-point (or a mixture of them) based models. In a second stage, high-level code is derived, either automatically from a model or manually. A second verification stage can be carried on, by using the generated fixed-point code in combination with discrete models. Afterwards, processor specific code (machine code) is derived through a compilation/linking process. At this stage processor-in-the-loop or hardware-in-the-loop simulations are used for verification. Figure 2.4 presents an overview of the design flow.

Because of the nature of software architectures, the designer does not have a direct influence on the underlying platform, but rather, the architecture and the algorithmic characteristics of the controller define the achievable performance.

Figure 2.4: Embedded software design flow

#### 2.1.2 ASIC-Based Design

An ASIC is an integrated circuit, which has been designed for a specific application. ASICs can be classified into three main categories: full-custom, semi-custom, and structured, as depicted in figure 2.2.

Full-custom ASICs are entirely fitted to an application, which implies that the designer can freely optimise the device in terms of area, time, and energy, thus reducing recurring component costs. Photo masks for all layers of the device, which are required for the photolithographic process of an ASIC production, have to be specified. This implies a increased production- and design-time. Thus, an increased price per device.

Semi-custom ASICs are designed based on predefined elements. Two kinds can be distinguished: standard-cell design, and gate-array design. Standard-cell ASICs are based on a pre-characterised collection of gates, which are typically provided by the manufacturer. The designer performs a very similar flow to that of full-custom ASICs, defining the placement and interconnection of the design, but instead of defining every gate, a standard library is used. Gate-array ASICs are constituted by pre-placed transistor-arrays. The device is customised by defining the local and global interconnect.

Structured ASICs (also known as Platform ASICs) are built from a sea of tiles, otherwise called modules, and a combination of embedded cores (such as memory

or I/O blocks). Tiles are logical elements, whose granularity varies from transistors to lookup-tables (LUTs). The internal interconnection of tiles is predefined, the designer has to define the interconnection of the tiles and the configuration of the existing embedded block (although much of the local and global interconnect is also predefined). This results in a shorter design- and production-time, in comparison with semi- and full-custom ASICs.

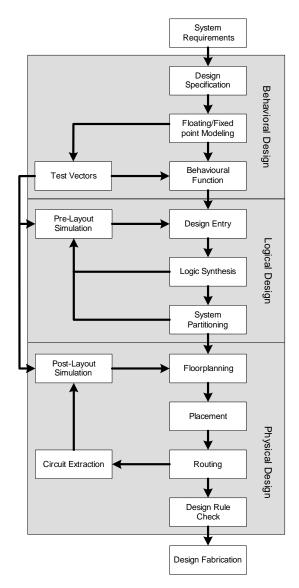

The design flow of ASICs varies depending on the target technology. However, the design can be split up into *behavioural design*, *logic design*, and *physical design*, as depicted in figure 2.5. The flow can be roughly described as follows:

Figure 2.5: Typical ASIC design flow [Nek03]

- System requirements: in this stage, the requirements of the design are sketched.

- Design Specification: formal specifications for the design are derived from the first stage.

- Floating/Fixed Point Modeling: a mathematical model is derived, focusing on the behavioural (mathematical) description of the algorithm, using either floating-point or fixed-point simulations.

- Test Vectors Generation: at this stage test vectors are generated, which are then used in the following verification steps.

- Behavioural Simulation: the mathematical description of the algorithm is verified, using behavioural simulations.

- Design Entry: the design is described by using either hardware description languages (e.g., VHDL, Verilog), or by using an schematic entry.

- Logic Synthesis: form the hardware description, a netlist is extracted, which is a structural model of the design containing references to logic cells.

- System Partitioning: the design, if required, is partitioned into many ASICs.

- Floorplanning: arranges the cells of the circuit and sets space for interconnect.

- Placement: sets the cell location in a block.

- Routing: creates the connections between cells and blocks

- Extraction (Back Annotation): determines the parasitic capacitance and resistance of the interconnect, vias, and contacts.

- Postlayout (Physical) Simulation: verifies the design with the information gained in the previous step.

- Design Rule Check: verifying that the circuit layout complies with the specification of the design rules.

### 2.2 Reconfigurable Hardware

Reconfigurable hardware, as opposed to CPU-based architectures, is constituted by several processing elements, whose function and interconnection are configurable. These hardware architectures can be categorised by using three main criteria: by the granularity of their building blocks, by the kind of reconfiguration, and by the diversity of their building blocks.

• Granularity: this classification refers to the size and complexity of the most basic computing element of an architecture. Fine-granular architectures allow bit level operations, medium-granular architectures allow operations with different number of bits, and coarse-grade architectures operate at the word level.

- Reconfiguration: two kinds of reconfiguration are distinguished, static reconfiguration, and dynamic reconfiguration, also known as run-time reconfiguration. The later allows a part of the device to be reconfigured while the rest operates, whereas the former requires execution to be stopped. Static configuration can be further classified in SRAM-based configuration, and Flash memory-based configuration. The former losses its configuration after power-off, while the later retains it.

- Block diversity: reconfigurable architectures can be constituted by a variety of computing blocks (e.g., lookup tables, embedded multipliers, etc.), or by a replication of the same basic computing element. The former kind is known as homogenous architecture, while the later is called heterogeneous.

This work focuses on Field Programmable Gate Array (FPGA) technology, which is a fine-granular, dynamically reconfigurable, and heterogeneous architecture. The main components of FPGA technology are introduced in the next section.

#### 2.2.1 Field Programmable Gate Array

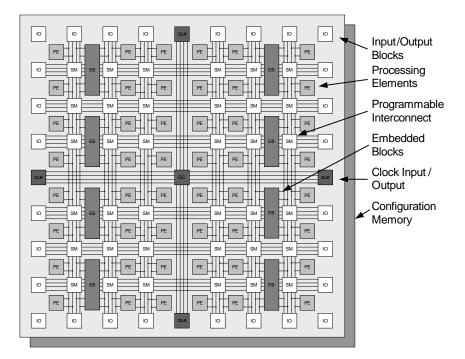

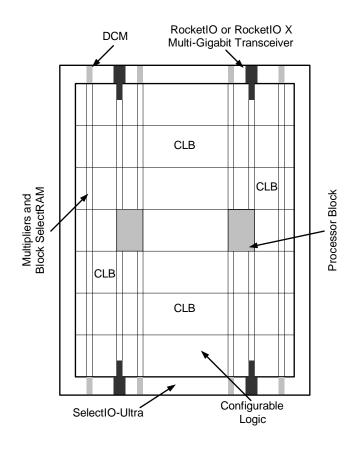

Nowadays there are several academic and commercially-available FPGA architectures. Most of them share the same set of basic elements, such as configurable logic blocks, I/O blocks, interconnect memory, embedded cores, clock management blocks, and configuration memory (see figure 2.6). In this section, these basic blocks are briefly introduced.

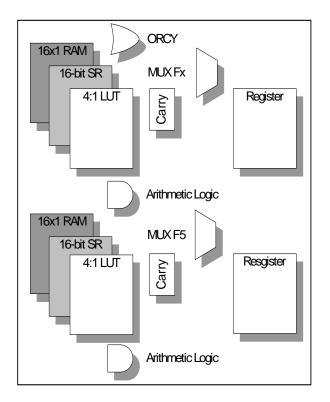

**Configurable Logic Blocks:** Configurable logic blocks (CLB) are the basic logic units of FPGAs. Typically, CLBs are composed of lookup tables (LUT), storage elements, multiplexers, and logic gates. The LUTs can be configured to realise any logical function, limited to the number of inputs and outputs of the LUT. Interconnect resources are used if more complex functions are required.

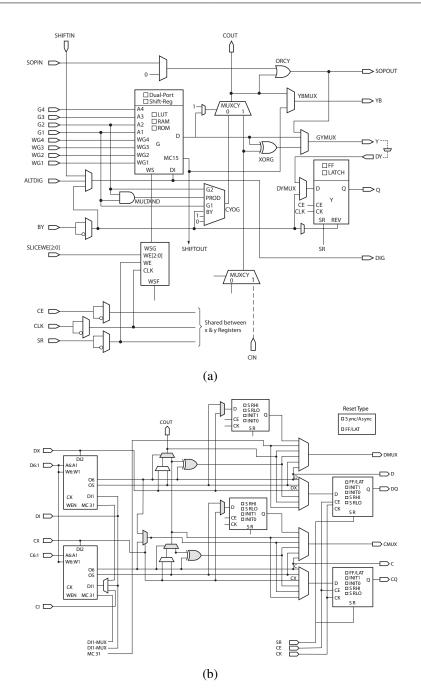

In the Virtex II architecture from Xilinx [Xil07b], a CLB is composed of four slices, which are the basic processing unit of FPGAs from Xilinx, plus interconnect resources. Each slice, shown in figure 2.7 is composed of two four-input one-output LUT, two flip-flops (FF), logic gates, multiplexers, carry chain logic for arithmetic functions, and a horizontal cascaded OR chain for implementing sum of products.

LUTs can be used as functions generators, as shift registers or as a RAM (Random Access Memory). CLBs are attached to interconnect resources, to build more complex functions.

**Configuration Memory:** FPGA resources are uncommitted, and must be configured to realise a digital design. There are mainly three basic types of configura-

Figure 2.6: Sketch of a typical FPGA architecture

tion approaches: SRAM based configuration, Nonvolatile-based configuration, and antifuse-based configuration.

Antifuse uses one-time programmable connections, whose impedance change on the application of a high voltage signal (the programming voltage). When the device is not configured, connections between blocks have very high impedance values (in order of Giga Ohms), so than the connection is virtually open. When the programming voltage is applied, connections fuse, reducing drastically their impedance to few ohms, thus establishing connections. The functionality of the device can not be changed after configuration.

Non-volatile configuration uses the same principle that EPROM (Erasable Programmable Read-Only Memory), EEPROM (Electrically Erasable Programmable Read Only Memory), or Flash memory use. Floating gate transistors are used to store configuration bits. Thus, configuration remains after power-off. These devices can be reconfigured to support a different functionality.

SRAM configuration uses volatile memory cells to store the configuration of the device. Pass-transistors or lookup tables can be used to configure the device. Since the configuration is volatile, an external memory is required to load the configuration file at power-up.

Figure 2.7: Simplified view of a Virtex II slice [Xil07b]

The Virtex FPGA family from Xilinx has an SRAM based configuration, allowing also partial configuration, which is one of the topics being investigated in this thesis. The configuration of Xilinx devices is further examined in chapter 4.

**Configurable I/O Blocks:** Input/Output blocks provide a bidirectional programmable interface between the FPGA and its peripheral environment. Basically, the I/O blocks can provide three states: input, output, and high-impedance. I/O blocks usually provide registers, in order to reduce the critical path between outside devices and the FPGA.

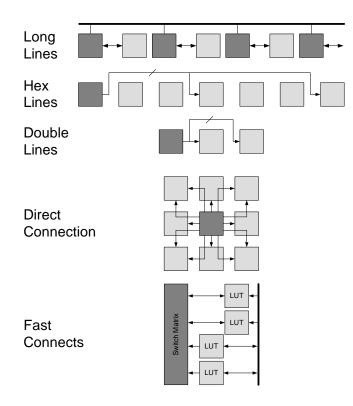

**Programmable Interconnect:** Programmable interconnection has a strong influence on the characteristics of the FPGA architecture. Programmable switches are used to realise connection between the different blocks of the FPGA and the routing resources. Typically, FPGAs have their routing resources organised as an island style, where the logic blocks are surrounded by a sea of routing resources, providing a high degree of flexibility (c.f. figure 2.6).

Figure 2.8: Hierarchical routing resources [Xil07b]

Let us consider the Virtex II FPGA as an example, whose hierarchical routing resources are depicted in figure 2.8. It has fast connects for internal CLB I/Os, direct connection to neighbouring blocks, vertical and horizontal double, hex and long lines.

**Clock Management:** FPGAs have dedicated clock resources, such as clock lines, buffers, multiplexers, and clock managers. Dedicated clock lines provide low-capacitance paths for clock signals. Clock buffers and multiplexers allow to halt or redirect clock signals. Digital Clock Managers (DCMs) provide a flexible control over clock frequency, phase shift and skew. The three most important functions of DCMs are to mitigate clock skew due to different arrival times of the clock signal, to generate a large range of clock frequencies derived from the system clock signal and, to shift the signal of all its output clock signals with respect to the input clock signal.

**Embedded ASIC Cores:** Modern FPGAs have, besides reconfigurable logic, embedded cores, such as multipliers, memory blocks, and processors. For example, some of the Virtex-II Pro devices have embedded PowerPC 405 RISC processors, high speed transceivers, dual port block-RAMs, Digital Clock Managers, and Multipliers, as depicted in figure 2.9.

Figure 2.9: Virtex-II Pro Generic Architecture Overview [Xil07c]

#### 2.2.2 General FPGA-Based Design Flow

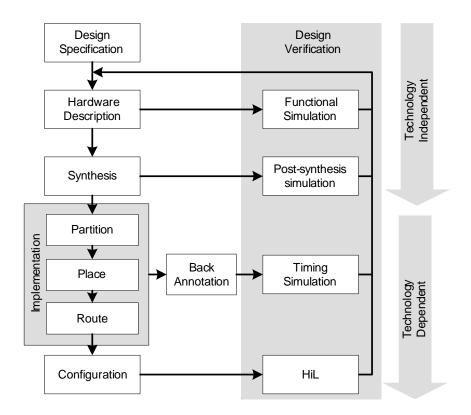

The design flow begins typically with the specifications of requirements and the definition of the functionality. Typically, a mathematical model of the design and its environment is derived from the previous steps and simulations are done using floating point precision (e.g., using Matlab/Simulink). From this high-level descriptions, hardware description is derived, as shown in figure 2.10. This step can be done using different hardware descriptions, ranging from traditional hardware description languages, such as VHDL or Verilog to C-like languages or schematic entries.

The choice of a hardware description has a great influence on the design developmenttime and resource-efficiency. A schematic hardware description such as System Generator from Xilinx [Sysb], or Synplify DSP from Synplicity [Synb] can lead to reduce the development time, without compromising resource-efficiency for digital control applications.

At this stage of the design flow, functional simulations are carried out to verify correct logic functionality. The next step is synthesis, where the design entry is translated from a functional description (e.g., VHDL) to a structural description (i.e.,

Figure 2.10: Typical FPGA-based design flow [Des06, Sim10]

netlist). Post synthesis simulations are done, to further verify the design. At this stage, technology-dependent steps take place, where the design is further synthesised, partitioned, placed, and routed, taking into account user-defined design constraints. This step is automatically done by vendor-specific synthesis tools. After these steps, post-place-and-route simulations are executed, which include more accurate timing information from the design. Typically, the design is at this stage ready to be loaded on the FPGA. A final verification step includes Hardware-in-the-Loop simulations, analysed in chapter 5.

## 2.3 Utilisation of Reconfigurable Hardware for Digital Control

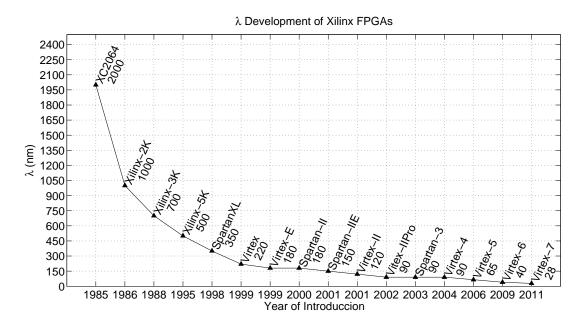

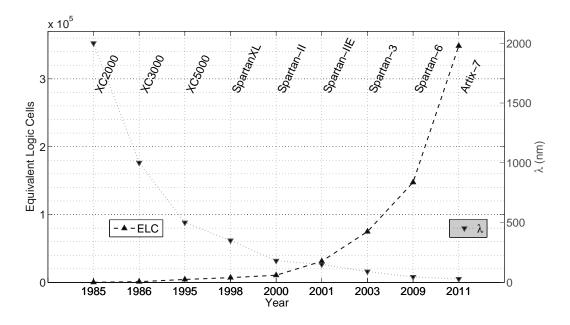

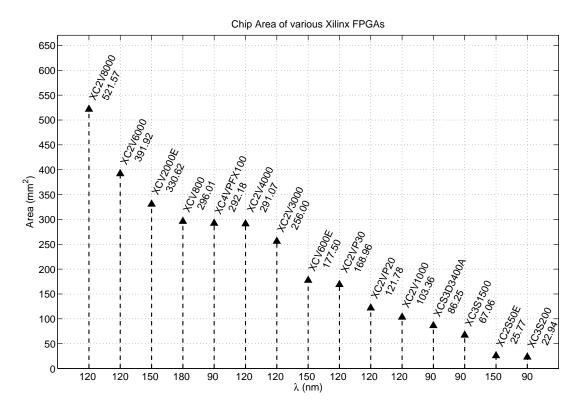

The use of reconfigurable hardware for digital control applications, not only as prototyping platform but as final target architecture, has been reported in literature since the early 90's. However, it is only until recently that researchers have started to show a greater interest in this technology, because of higher computational demands of digital control systems, and the fast evolution undergone by FPGAs in the last decades. Figures 2.11 and 2.12 present two aspects of the evolution of FPGAs; the reduction of the minimum feature size, also known as  $\lambda$  (cf. figure 2.11). Figure 2.12 shows a logical consequence of the reduction of  $\lambda$ , namely the increase of equivalent logic cell per device, which enables the realisation of complex control schemes.

There are also other aspects of FPGA technology that have drastically evolved during the last decades, such as the basic logic cells themselves, the integration of embedded ASICs (e.g., processor cores) into the reconfigurable logic, or improvement of software tools to map digital designs onto this technology, as presented in section 2.2. How this evolution has impact the view on this technology, producing a technology migration, which has taken FPGA from rapid prototyping platforms to target devices [5], is analysed in the following sections, pointing out specific examples from literature and classifying the factors that contributed to adopt FPGA technology for control applications.

#### 2.3.1 Application Spectrum

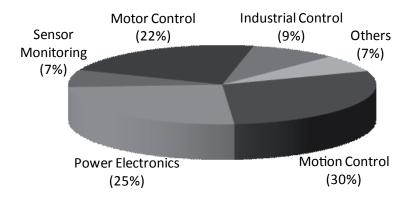

In literature, the reported application spectrum is very wide. However, three main areas can be distinguished: direct motor control, power electronics and motion control, as depicted in figure 2.13. Motor control refers to the direct manipulation of a DC or AC motor inputs (e.g., voltage or current) to obtain a specific torque, position or speed (for a review on this application domain see [Mon02a]). Power electronics deals with the implementation of control strategies for DC-AC, AC-DC, or DC-DC

Figure 2.11: Overview of the development of the feature size of FPGAs from Xilinx

Figure 2.12: Overview of the development of Low-cost FPGAs from Xilinx

converters. Motion control refers to the implementation of algorithms for obstacle avoidance, acceleration profile generation, or route planning, usually related to robotics or Computerised Numerically Control (CNC) machines.

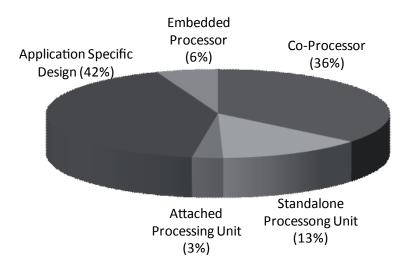

Figure 2.13: Application distribution of the reviewed papers

The utilisation of Reconfigurable Hardware (RH) to implement industrial controllers for production lines as replacement of Programmable Logic Controllers (PLC) is also presented in literature. Furthermore, publications reporting sensor monitoring applications were reviewed, where the main focus is the hardware-based implementation of algorithms to process data from sensors. Other applications include the realisation of fuzzy controllers for temperature control [Jua05], PID-based control of an electrostatic levitation system [Nak02], or embedded controllers for automotive applications [Chu02].

In the reviewed articles (more than 100 papers from many scientific journals and conference proceedings), many authors report the use of FPGAs instead of traditional platforms. The reasons are analysed in the following section.

#### 2.3.2 Factors of the Technology Migration

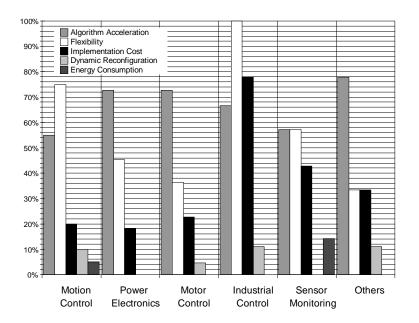

The utilisation of FPGAs instead of other architectures is mainly based on four factors: the acceleration of the design or parts of it, the flexibility of reconfigurable hardware, the reduction of development costs, and energy consumption. These factors have a different effect on each application area, as depicted in figure 2.14.

Figure 2.14: Distribution of the contributing factors of FPGAs in the application spectrum

In the review process, a score was given to each factor per publication. Therefore, one publication might report more than one contributing factor. The use of run-time hardware reconfiguration is also included in figure 2.14, and is analysed in section 2.3.4. The reported effect of each factor on the implementation of digital controllers is analysed in the following section, giving specific examples.

#### **Controller Acceleration**

Using reconfigurable hardware to accelerate algorithms has been extensively reported (e.g., for digital signal processing [Tes01]). In 58% of the reviewed papers, algorithm acceleration is described as one of the main contributions of RH to the implementation of digital controllers. The term acceleration implies a faster hardware or hardware/software (Hw/Sw) realisation of a given design in contrast to a software equivalent. This was achieved through different means, such as parallel processing, reduction of the computation overhead or heavily pipelined realisations. For realisations using Hw/Sw partitioning on-chip co-processing was exploited.

**Parallel Processing.** In contrast to software architectures (e.g., processors), a hardware realisation with various processing elements operating in parallel can achieve a better performance. However, the extent in which this feature can be exploited is highly dependent on the intrinsic parallelism of the algorithm to be realised. Therefore, it is meaningful to detect the amount of concurrency in early stages of the design flow [Nao04, Cha04].

Parallel processing was used in applications such as stepper motor control [Car03]. The utilisation of a Xilinx XC4006 FPGA resulted in an increment of the reachable motor speed due to a faster processing. The required sampling period was 800 ns and the clock frequency was set to 40 MHz. In [Zum03] parallel processing was used to accelerate a digital controller of an AC-DC Converter using a Xilinx XC4010 FPGA with a clock frequency of 20 MHz. To realise the same design using DSP technology, a much higher clock frequency would have been required. A similar approach was presented in [Her04] to process information from an ultrasonic ranging sensor. A Xilinx XCV1000E FPGA was used to implement the algorithm, achieving a sampling period of 235 µs at a clock frequency of 50 MHz. The availability of independent processing elements in combination with embedded processors, embedded multipliers units and block RAM made possible the realisation of distributed computation, leading to the reported algorithm acceleration. A similar approach was presented in [Yao10] for speed control of turbines. A PID-Fuzzy controller was implemented, reaching execution times well beyond CPU-based realisations. A direct hardware realisation of a Fuzzy controller was reported in [Che11], for a DC-DC controller of a photovoltaic system.

**Reduced Computation Overhead.** The utilisation of dedicated hardware reduces the required computation overhead of general purpose architectures. Moreover, many operations, such as bit shifting or multiplication and division by a power of two, are done implicitly when realising them in hardware.

Design specialization was used in [Ada00] to implement industrial controllers as a replacement of Programmable Logic Controllers. In [He04], application specific hardware accelerated a controller for a robotic hand with multiple motors. By using a combination of dedicated hardware and software it was possible to achieve a sampling period of 200  $\mu$ s having a clock frequency of 150 MHz. The FPGA implementation of an iterative algorithm for time optimal control (TOC) of AC drives was presented in [Bol04]. The utilisation of an Altera EP20K200EFC484-2X with a sampling rate of 16  $\mu$ s at a clock frequency of 2.2 MHz allowed the realisation of time-critical parts (e.g., equations including trigonometric operations) of the TOC algorithm in hardware to accelerate the design.

Implementation of specialised processors for control algorithms was presented in [CP01]. A specialised architecture to realise state-space based controllers was reported. This architecture outperformed various commercially available DSPs and required a low gate count for its implementation. A similar approach was presented in [MV10b] for motion controllers of CNC machines. A specialised processor architecture allow a better performance than DSP- and PC-based realisations.

For designs requiring Hw/Sw partitioning the utilisation of soft-core processors (e.g., MicroBlaze from Xilinx) reduced the communication overhead, in comparison to systems with external chip couplings. Although the reported designs used only soft-core processors, modern FPGAs integrate embedded hard-wired processors and DSP units (e.g., the Virtex-II Pro FPGA from Xilinx, with two PPC processors and 192 18x18 hard-wired MAC units), which can achieve higher clock frequencies than their soft-core counterparts. In addition to block RAM, configurable logic can be used as memory. Thus reducing overhead, in comparison to a scheme in which data has to be stored off-chip.

On-chip co-processing was used for motion control of autonomous mini-robots [Rog03] where the soft-core RISC processor NIOS was used to perform various control-flow oriented operations, such as network monitoring and interfacing. In [Pou04] an adaptable thermal compensation system for strain gage sensors was presented. A NIOS processor was used to perform floating point arithmetic operations. Robotic arm manipulation [Kun05] was performed using an Altera Stratix EP1S10 FPGA. A NIOS processor was used to realise those parts of the position control algorithm that required a low sampling frequency. Similarly, in [BO10] the realisation of a PID-controller as hardware accelerator of a multi-processor on chip (MPoC) architecture for motor control was presented. A similar approach was presented in [Kun10] for motion control of a three-axis wafer-handling robot.

Heavily Pipelined Realisations. This factor can augment the throughput of a design at the cost of introducing some time-delay and using more hardware resources. This technique was used in applications such as current vector control of AC machines [Taz99], where a sampling period of 50  $\mu$ s was obtained. A pipelined realisation was also used for image processing for robotic motion control [Bol01]. 285 images per second, of 9728 pixels each, could be processed during 60 ns as part of a motion

detection algorithm. According to the authors, the achieved performance could be easily improved by adding more stages to the pipeline.

#### Flexibility

An architecture is said to be flexible if it can be modified to meet new requirements. This feature is usually related to software architectures, where such an adaptation is done by replacing the instructions controlling the central processing unit (e.g., an ALU). This feature is called programmability. Flexibility is then mostly related to the binding time of a given architecture, that is, the time when the functionality of a device is specified. Describing the architecture spectrum as a function of its binding time, one extreme would be occupied by pre-fabrication operation binding devices (e.g., ASICs) and the other extreme by cycle-to-cycle operation binding devices (e.g., processors)[DeH99]. SRAM-based FPGA technology is considered to be flexible because it has a late binding time. (cf. figure 2.15).

|         | "Hardwar                   | e"            |                               | "Software"            |                |  |

|---------|----------------------------|---------------|-------------------------------|-----------------------|----------------|--|

| Media   | Custom<br>VLSI             | Gate<br>Array | One Time<br>Program_<br>mable | FPGA                  | Processors     |  |

| Binding | <i>Time:</i> First<br>Mask | Metal<br>Mask | Fuse<br>Program               | Load<br>Configuration | Every<br>Cycle |  |

Figure 2.15: Binding time continuum [DeH99]

Flexibility was one of the most reported features of RH; 54% of the publications reported flexibility as a deciding factor to have chosen RH as implementation platform. However, not all authors defined flexibility in the same way. Two factors were considered in this review as contributing to make RH a flexible platform: hardware reconfiguration and the possibility to realise Hw/Sw partitioning on the same platform.

Hardware Reconfiguration. The more specialised an architecture is, the more efficient it performs. However, changes in the application can strongly lower the reachable performance, even for general purpose architectures with a certain level of specialization. DSPs are a good example. They were originally designed to couple with operations in which the same operands are applied to a certain number of values (vector operations). When required to execute operations such as look-up tables, tree searches, or sum of absolute differences, these specialised units (e.g., MAC units) can not be optimally exploited, resulting in a loss of performance. In this sense, the algorithm has to be adapted to meet specific processor architectural characteristics.

Like general purpose processors, RH architectures have a late binding time. This allows the adaptation of reconfigurable devices to the application [Ada00, Sag04, Rue03a, Che02, Li03, Cho01, Che00], usually reaching a better performance than a software equivalent. If the application should change, the new requirements can be handled by accordingly reconfiguring the design [Tho99, Her04, Kou05, Kel97], optimizing it to different possible situations [Bol01, Cho01, Yin04, Ric03]. The precision (e.g., the bit-width) of the design can be changed [Fan05] accordingly to the requirements, making the design scalable [Dep04]. There are spatial limitations (e.g., chip area) that constraint the complexity (e.g., the necessary resources) of a design that can be implemented on a RH platform. However, there are also methods that help to overcome this limitation. Namely, run-time reconfiguration [2, 3, 6, 7, Nas04, He04, Chu02, Dan03a, Dan03b], analysed in section 2.3.4, and in detail in chapter 4. This feature gives a new degree of freedom to the design space of embedded systems, since it is possible to trade speed and area in run-time.

**On-Chip Hw/Sw Realisation**. FPGAs allow a Hw/Sw realisation on a single chip. This is possible by using configurable logic to realise dedicated hardware in combination to embedded soft- or hard-wired processors. This feature opens new possibilities in the design-space, offering a higher level of flexibility than pure hardware or pure software platforms. Parts of a control algorithm having high diversity of operations and requiring a low sampling frequency are better implemented in software, while other computational intensive parts of the algorithm are better implemented as a dedicated hardware. In [Kun05] Hw/Sw partitioning was used to realise an architecture for robot arm control, or in [Cab04] to implement fuzzy controllers. Similar approaches were presented in [Pou04, Rog03, Pat10b, Pat10a, Kun10]. Furthermore, by using run-time reconfiguration (see section 2.3.4), the Hw/Sw partitioning can be adjusted dynamically (software tasks can be realised as hardware tasks and vice versa), in order to adapt the resource-availability to the requirements of the system, as suggested in [3] for robotic applications (this topic is analysed in chapter 4).

#### Costs

Having specific requirements for a given application, such as a minimum sampling rate or a desired functionality, the choice of an implementation platform is a matter of finding a suitable compromise of the factors involved in the design process, e.g., total price, performance, or safety. The cost was reported in 31% of the reviewed papers as an important reason to use RH instead of other technologies. In 46% of those papers the comparison was against DSPs, 9% against PLCs, 7% against general purpose processors, and 38% did not report the replaced technology. The key factors for preferring RH are the cost/performance ratio, hardware description, time-to-market and development cost. These factors are analyzed in the following sections.

**Cost/Performance Ratio.** Considering not only the price of a single device when choosing the implementation platform, but the cost/performance ratio [Nas04, CP01]. It was shown that although a single FPGA chip might be more expensive than a single DSP, the performance that the former can reach is potentially grater [Tom04, Rey04] leading to an overall lower price when considering how many DSP units would be needed to reach the same performance.

Berkeley Design Technology Inc (BDTI) made an analysis based on an orthogonal frequency division multiplexing (OFDM) benchmark [Alt05], in which two Altera FPGAs, the Stratix 1S20-6 and the IS80-6, and a Motorola MSC8101 DSP were compared. The report showed a better cost/performance of the FPGAs, despite the fact that the DSP had a lower cost than both FPGAs.

Cost/performance ratio was reduced by the use of specialised design techniques, which allowed the utilisation of cheaper devices for the implementation. In [MI04] a control algorithm for a switching DC converter was realised using FPGA technology. Because of the specialisation of the design, it was possible to replace a high-resolution ADC converter, required for most DSP calculations, with comparators, leading to an overall price reduction. A similar approach was presented in [Ben99] for high-performance thyristor gate control for line-commutated converters. The design specialization leaded to a low-cost FPGA implementation, avoiding the use of several DSPs. Similar implementations were presented in [Don03]; the use of specialised hardware designs (e.g., a parallel FPGA implementation) allows the utilisation of simpler RH architectures, which are often cheaper than a corresponding softwarebased solution. Furthermore, the specialisation of a soft-core processor presented in [MV10b], allowed the realisation of a system identification algorithm for a motion controller of a CNC machine.

Hardware Description. The design of controllers for general purpose processors or DSPs usually starts with an abstract, high-level design entry (e.g., C code), which is then translated automatically into an executable format. This tool flow enables the design engineer to focus on the control algorithms without having to deal with the underlying architecture. Expert programmers can optimized critical parts of the design by manually inserting lower level code (e.g., assembly code). Hardware description can also be realised at different abstraction levels; from a register transfer level (RTL) to a behavioural description by using languages such as VHDL or Verilog [Zum03, Aco02, Rei03], providing technology independence [Mat05, Bol04]. Hardware Description Languages (HDL) might not be suited for engineers already used to the design flow of software architectures. For such engineers there are various C-like HDLs [Tom04, Aco02], such as System-C [Sysa], or Handel-C from Celoxica [Han], which integrate the necessary features to describe hardware (e.g., parallel constructs). These HDLs are supported by compilers and synthesis tools, providing a way to generate either VHDL code or netlists from the original script.

In the last decade, several manufacturers of configurable hardware introduced veryhigh-level hardware descriptions, such as System Generator from Xilinx [Xil08c], DSP Builder from Altera [DSP] or Synplify DSP from Synopsys [Synb], which can be used within Matlab/Simulink. Outcome of these design flows is a structural description of the design, which can be mapped (synthesized) onto an FPGA. Such hardware descriptions provide a higher abstraction level than traditional HDLs and C-like HDLs, thus reducing the design effort [2, Nao04, Cha05b].

The utilisation of Intellectual Property (IP) cores, visual programming languages, and designs reusability methods facilitate the implementation of complex system on chip (SoC)[Don03, Old05, Rey04]. Hardware description has a direct impact on the design effort required to complete a design. This in turn influences the required time-to-market (TTM), which is discussed in the next section.

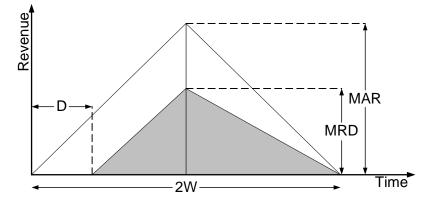

**Time to Market**. Introducing a product late into the market could lead to a potentially lower revenue. A simplified model presented in figure 2.16 suggests that the lost can be estimated by the equation 2.3 [Des06].

Figure 2.16: Cost of delayed entry into a market [Des06]

$$MRD = \frac{D(3W - D)}{2W^2}MAR$$

(2.3)

Where: *D* is the delay, *W* is half of the production life-span, *MAR* is the maximum available revenue, *MRD* is the maximum revenue from a delayed entry. As an example, if a product *A* has a lifespan of 3 years (36 months) with an estimated *MAR* = 50MD and has a delay of 3 months, the cost of that delay is a loss of 23.61% of the original revenues estimate, that is a *MRD*  $\cong$  38.2MD. In literature it was claimed that the use of RH can potentially avoid a late product delivery.

It was said that when using RH, TTM can be drastically reduced in comparison to an ASIC lead-time. The exclusion of some design steps inherent to the ASIC fabrication (e.g., mask generation, silicon fab, silicon verify) and the parallelisation of software and hardware development due to early system prototyping enables the reduction of TTM. This allows a quick implementation of complex algorithms [Ho00] resulting in a shorter TTM [Aco02, Kim00]. TTM has been further reduced by the introduction of intellectual property (IP) blocks [Bol04], and high abstraction level HDLs (see discussion in section 2.3.2), which allows the integration of optimized ready-to-use blocks into the design. A modular design strategy [Cha04] also contributes to shorten the design time, and thus reach a shorter TTM.

Design verification is time- and resources-consuming. The total cost of verifying the functionality of a design might by shortened by the introduction of Hardware-in-the-Loop (HIL) simulations [Ise99]. For software based designs, this technique has reduced the gap between controller design and implementation in the final platform. For FPGA-based controllers, the principles of HIL can also be exploited, resulting in a speedup of the simulation process and providing a cycle accurate verification of the design [4]. This topic is further analysed in chapter 5.

For high-performance applications, for which using many CPUs concurrently to reach a desired throughput is required, two situations can arise: the overall development cost increases due to the utilised extra processing units and the software routines that allow multi-tasking and parallel processing become difficult to handle [Mon99]. Depending on the engineer expertise, this situation could lead to a longer design cycle than expected.

**Development Costs.** When using RH, it is possible to realise most of the required functional blocks on the same chip, which avoids to use many discrete elements [RT04, Car03, OR09, OR08], and reduces the required board size and the energy consumption [Kel97]. The availability of low-cost and large-capacity FPGAs, an increasing number of intellectual property (IP) modules, and powerful CAD tools enables the development of a whole system on programmable chip (SoPC) [Cab04, Pat10b, Pat10a].

This technique was used in [Rue03a] to implement an FPGA-based emulator for series of multi-cell converters. The integration of observers in the design permitted a sensorless implementation, reducing the overall cost. Similarly, in [Kun05] the utilisation of FPGA technology allowed the implementation of all necessary computing elements to control a vertical articulated robot arm. In [Li03] this approach was used to implement an FPGA-based fuzzy behavior control for an autonomous mobile robot.

The development costs of RH-based realisations was also compared to that of ASIC realisations [Aco02, Chu02], which were avoided because of the implicated high costs for low-quantity productions. In [Old05, Old01] an FPGA-based servo control was

presented. The advantage of FPGAs was said to be that custom parallel processing architectures can be embedded on a single device, without incurring the high NRE costs and re-spins associated with ASIC development, for low-quantity productions.

#### **Energy Consumption**

The energy consumption of a system may be a critical factor when choosing an implementation architecture, specially for systems running on limited energy supplies (e.g., batteries) or with heat dissipation constraints. When using CMOS technology the total account of energy consumption depends on the static and dynamic power dissipation. The main cause of static power dissipation is leakage, which is largely determined by the device type, operating temperature and process variations. The dynamic power consumption is completely design-dependent, and is determined by factors including resource utilisation, logic partition, mapping, placement and routing. The designer has influence mainly on the dynamic power dissipation. Due to the energy overhead required for routing resources and configuration memory FPGA-based designs have a higher power dissipation than ASICs.

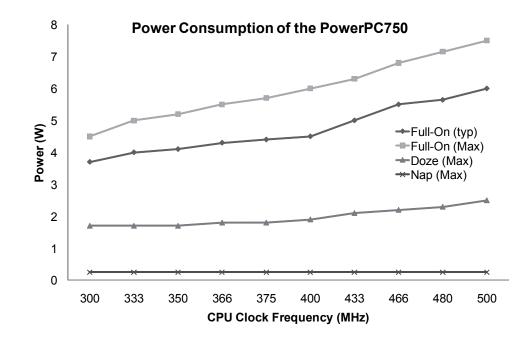

In [Kel97], a methodology was presented to implement state-space based controllers using FPGA technology. The use of this technology was said to reduce the energy consumption by 50% when compared to designs built out of many integrated circuits, because the capacitive loads were lowered. In [Scr02] a comparative study of the energy efficiency of FPGAs and programmable processors for  $n \times n$  matrix multiplication was presented. The measurements showed that a Virtex-II Pro FPGA (from Xilinx) achieved the shortest latency and used less energy than a TMS320C6415 (from Texas Instruments) and a PXA250 (from Intel) for this specific task. However, the Virtex-II Pro performed the worst under a different configuration. Energy consumption of FPGA-based designs is further analysed in chapter 3.

# 2.3.3 Coupling of Reconfigurable Hardware and Software Architectures

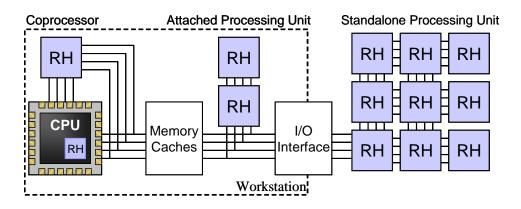

For applications with Hw/Sw partitioning, RH can be classified according to its levels of communication as: co-processor, attached processing unit, standalone processing unit, or RH with embedded processor [Tod05] [Com02] as depicted in figure 2.17.

Although the majority of the reported works were implemented as application specific designs (42 %, see figure 2.18), the use of Hw/Sw partitioning was a widespread design approach. Each kind of coupling is described in the following sections.

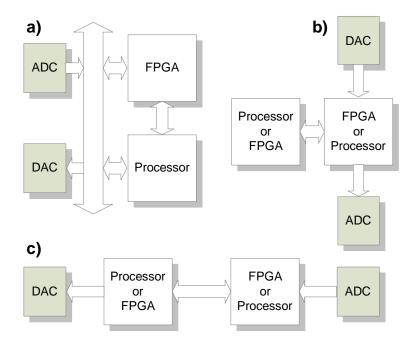

Figure 2.17: Different levels of coupling in a reconfigurable system[Com02]

#### RH as a Coprocessor

In this kind of coupling, RH is able to perform operations without the constant supervision of a host processor. Usually RH is used to realise computational intensive operation and sends the resulting information to the host processor. This generally allows the processor and RH to run parallelly. Examples of this approach are a position measurement algorithm, reported in [Lyg98], in which an Altera FLEX was coupled with a Texas Instruments (TI) DSP TMS 320C31. In [Jun99], a PWM controller for DC/AC converter was realised in a Xilinx XC4005 and coupled to a TI DSP TMS 320C14. Moreover, an algorithm for adaptive motion control, described in [Gwa02]

Figure 2.18: Classification of reconfigurable hardware according to the reported coupling

was realised in a Xilinx XCV300 coupled to a DSP. In the aforementioned publications the DSP unit realised control flow oriented task (e.g., monitoring).

Figure 2.19: Reconfigurable hardware and processor couplings in reference to the I/Os. a) Processor and FPGA have access to the ADC and DAC. b) Either an FPGA or a Processor is directly connected to the ADC and DAC with a tight communication with the other processing element. c) Either a Processor or an FPGA receive information form ADC and the other processing element is connected to the DAC.

There were different co-processor configurations in which RH and software architectures were coupled as depicted in figure 2.19. In configuration (a) both processor and RH have the same level of connectivity to the I/Os. This makes the partitioning of hardware and software tasks more flexible. In configuration (b) the architecture connected to the I/Os (either RH or a software platform) performs most of the control tasks, assigning the other device to supervisory tasks. In most of the reviewed papers, an FPGA was directly connected to the I/Os. In configuration (c) the device connected to the inputs realises data conditioning tasks (e.g., units transformations, data scaling, digital filtering). The device connected to the outputs realises most of the control tasks. In the majority of the reviewed papers a processor was connected to the inputs and an FPGA to the outputs.

#### Attached Processing Unit

In this kind of coupling the communication between RH and the host processor is less frequent than in the previous kind. Usually RH was used to execute parts of the controller, an then either to send information back or to send a command directly to the plant. FPGAs were used in [Din05] to generate high-frequency PWM signals for a voltage-source-converter-based distribution static compensator. A DSP (TMS320C40 from TI) was coupled with an FPGA (FLEX8000 from Altera) via a bus system. The control system was implemented using the DSP and the multiple-PWM generator was implemented in the FPGA together with a dead-time insertion module. The data exchange was limited to the required duty-cycle. A similar approach was reported in [Faa04]. The utilisation of radial functions neural networks (RFNN) to implement a sensorless motion control algorithm for spindle motors was presented. A synchronous PWM with dead-time compensator was done in a Xilinx FPGA, which was coupled to a Pentium-based PC. Another example was reported in [Jia02]. The implementation of a servo drive for an ultrasonic motor was presented. The controller was implemented in an Altera 10K100 FPGA, which was coupled to a Pentium II-based PC. The communication between PC and the FPGA board was limited to supervisory tasks.

#### Stand Alone Processing Unit

This is the loosest coupling. The communication between the host processor and RH happens infrequently. It can be compared to the kind of communication among workstations in a network. An example was presented in [Han02], in which the implementation of a genetic algorithm to set up a neural-controller was realised on several Altera FLEX EPF8452 FPGAs, coordinated by a PC. Another multi-FPGAs design was presented in [Bol01]. Several FPGAs were used simultaneously to realize an image processing algorithm for movement detection, used in a mobile robot. A Pentium-based PC coordinated the computations realized on the FPGAs. The use of RH allowed the acceleration of the computational intensive image processing algorithm.

#### RH with Embedded Processors

Another approach to Hw/Sw design was to include an embedded soft-core processor instead of an external unit. The integration of the processor inside the FPGA reduced communication overhead, costs and board size, as discussed in section 2.3.2.

Hw/Sw partitioning of the implemented design was often reported in literature. The method to realise the partitioning was rarely mentioned. However, it was observed that in general control flow operations, such as variable-length loops or branch control were realised using a software platform, for instance operations whose hardware

Figure 2.20: Reported reconfiguration types for digital control applications

implementation were too expensive (e.g., floating point arithmetic). Parts of the algorithm, which could be benefited from a hardware implementation, such as fixed path operations or parallel operations, were implemented in reconfigurable logic.

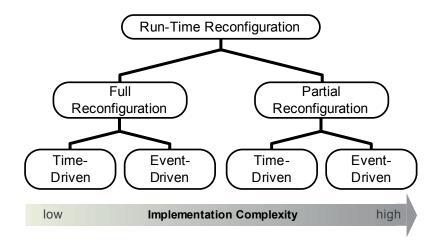

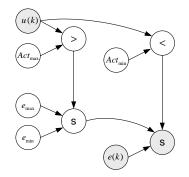

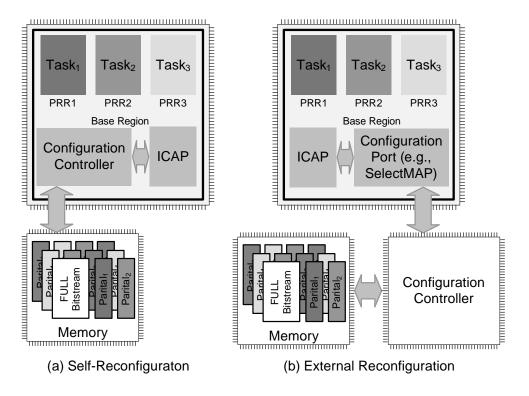

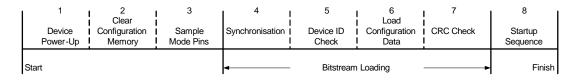

#### 2.3.4 Run-Time Hardware Reconfiguration

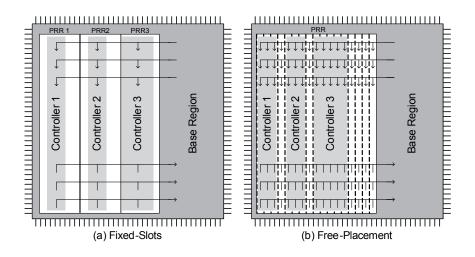

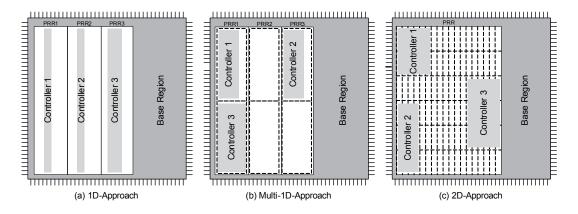

Run-time reconfiguration (RTR) is a scheme in which an FPGA is partially or fully reconfigured during the execution of a task, where a task consists of one or more sub-modules. When the FPGA is only partially reconfigured the process is called *partial run-time reconfiguration* or *dynamic reconfiguration* (DR). Both full RTR and DR can be used to enhance the resource-utilisation of an FPGA by time-sharing logical resources among non-periodic designs (*event-driven* reconfiguration) or by periodically time-multiplexing sub-modules of a design (*fixed schedule*) [3].

A classification of RTR schemes used to implement digital controllers is depicted in figure 2.20. The realisation of a RTR architecture becomes more complex depending on the reconfiguration kind (full or partial), and the reconfiguration scheme (*fixed schedule* or *event-driven*)

#### Fixed Schedule RTR

In this scheme a design is partitioned in sub-modules, which are loaded on the FPGA periodically in a pre-defined sequence. This scheme was used in [Kim00] to implement fuzzy controllers. The authors divided the design into many temporally independent functional modules and performed full RTR sequentially with the bitstreams corresponding to each module, saving intermediate results in an on-board SRAM. Each module contained an SRAM interface and a bus interface. The reconfiguration was

controlled by a host computer. In [Nas04] DR was used to implement a controller for an elevator using the *fixed schedule* scheme. The FPGA was divided into a static and a dynamically reconfigurable area. Intermediate results were stored in a register bank of the static area.

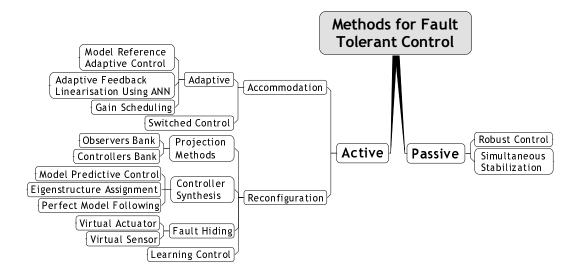

#### **Event-Driven RTR**

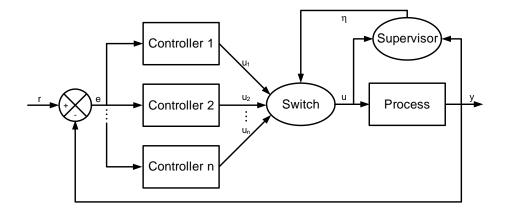

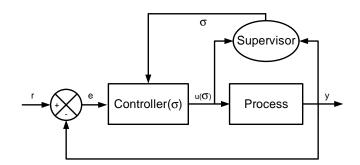

In this scheme the reconfiguration time is not known during the design phase, requiring the implementation of a more complex configuration manager. In [Vas04] *event-driven* full RTR was suggested to implement a fault tolerant control system for AC Drives fed by tandem converters. Full RTR was chosen because of the technological complications of realizing partial RTR. *Event-driven* partial RTR was used in [Dan03b] to implement a multi-controller approach for linear time-invariant systems. The configuration of the FPGA was realised via a host computer. In [Tos05] the use of this scheme to implement the controller of systems having different functions (e.g., normal operation, test, etc.) was suggested. Another approach was presented in [Chu02], where *event-driven* partial RTR was used to implement a fault tolerant controller for automotive applications. An architecture including a reconfiguration controller, memory to store partial bitstreams, and a module to switch between controllers was presented.

Although the potential benefits of using DR are known, this scheme is still largely unexplored for control applications, and constitutes one of the research points of the present work. In chapter 4, this topic is analysed in detail, addressing topics such as resource utilisation, control disturbances, and showing case-studies.

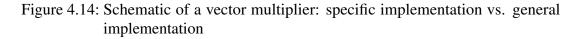

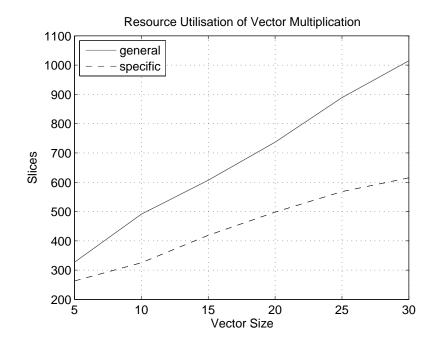

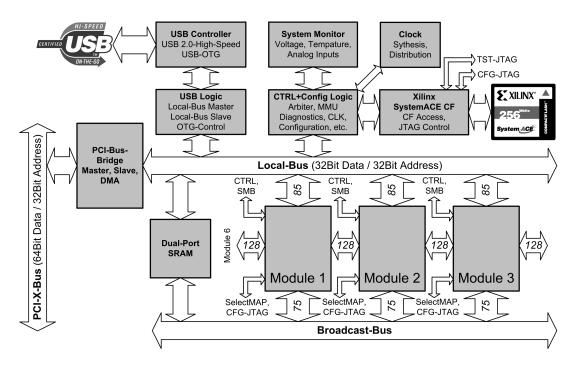

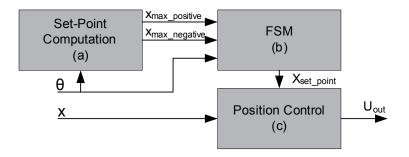

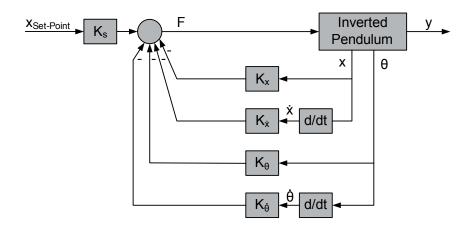

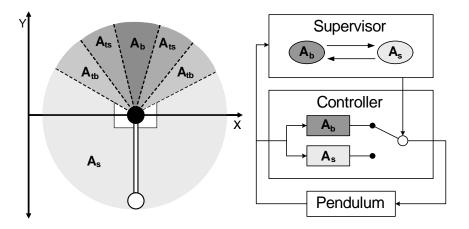

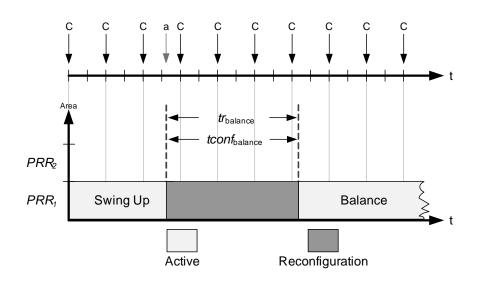

# 2.4 Summary