#### Exzellenzcluster Cognitive Interaction Technology

Kognitronik und Sensorik Prof. Dr.-Ing. U. Rückert

# Run-time reconfigurable, fault-tolerant FPGA systems for space applications

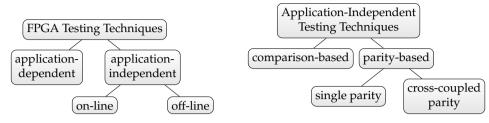

zur Erlangung des akademischen Grades eines

DOKTOR-INGENIEUR (Dr.-Ing.)

der Technischen Fakultät der Universität Bielefeld

genehmigte Dissertation

von

M.Sc. Dario Cozzi

Referent: Prof. Dr.-Ing. Ulrich Rückert Korreferent: Prof. Cinzia Bernardeschi

# **Acknowledgment**

This is a fantastic and important achievement of my career. I have to thank a huge number of people for all the tips, experience, and support that they have provided me during this path.

I should primarily thank the people that have followed me during all my PhD path. I thank Prof. Dr.-Ing. Ulrich Rückert and Dr. Ing. Mario Porrmann that have supported me and they have provided me a huge amount of experiences. I thank Jens Hagemeyer for the great and unlimited support for the problems (challenge) that I have encountered in my path. I thank Sebastian Korf, for his friendship, collaboration, and support in all the work that we have made together.

I thank Prof. Cinzia Bernarderschi, who accepted to review my thesis and for the collaboration that we have had in all these years. I thank the member of the examination commission JProf. Dr. Elisabetta Chicca and Dr. rer. nat. Robert Haschke.

I thank all the KS group, all my colleagues. It has been extremely motivating to work with you all. We have shared funny moments and you contributed to expand my career knowledge. In particular, I thank Dirk Jungewelter, Martin Kaiser, and René Griessl. Special thanks to my colleague/friend Luca Cassano that has deeply contributed to my academic career.

I thank all the students that I have supervised, which have been fundamental for my research: Dominik Kleibrink, Timo Schlüssler, Martin Vorfeld, Domenico Sorrenti, Luca Santangelo, and Filippo Mascolo.

I want to thank all the little-Italy community of Bielefeld. I have shared with you a lot of fully moments. I just mention one name for everyone: Giorgio Ferrari. Of course, I thank Paderborn and all its people because it is there where all the story started.

At this point of my career, I extremely feel how all the educators, professors, and teachers have contributed in a unique way on my knowledge and preparation. Thanks to all of you.

I extremely thank my parents Enrico and Serenella, for the support, critics, and motivation in all my life. I am really grateful to you both.

Any effort has no sense without love! I thank my fantastic wife Natalia and my little princess Eleonora. You have been always by my side. This achievement is for you.

Dario Cozzi Bielefeld, Germany

#### **Abstract**

The aim of this thesis is to investigate the use of Dynamic Partial Reconfiguration (DPR) on Commercial Off-the-Shelf (COTS) FPGAs in space applications.

Reconfigurable systems gained interest in a wide range of application fields, including aerospace, where electronic devices are exposed to a harsh working environment. COTS SRAM-based FPGA devices represent an interesting hardware platform for this kind of systems since they combine low cost with the possibility to utilize state-of-the-art processing power as well as the flexibility of reconfigurable hardware. FPGA architectures have high computational power and thanks to their ability to be reconfigured at run-time, they became interesting candidates for payload processing in space applications.

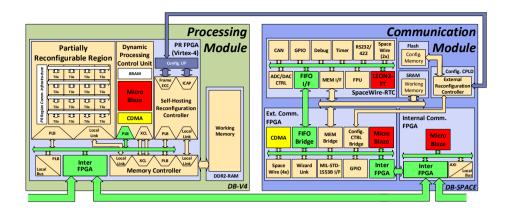

The presented Dynamic Reconfigurable Processing Module (DRPM) has been developed to investigate the use of the DPR approach for satellite payload processing. This scalable platform combines dynamically reconfigurable FPGAs with the required avionic interfaces (e.g., SpaceWire, MIL-STD-1553B, and SpaceFibre). In particular, a novel communication interface has been developed, the Heterogeneous Multi Processor Communication Interface (HMPCI), which allows inter-process communication with small latency and low memory footprint.

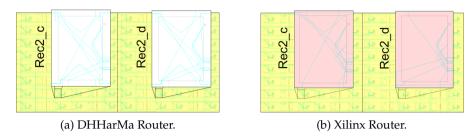

Current synthesis tools do not support fully the DPR capabilities of FPGAs. Therefore, this thesis introduces INDRA 2.0: an INtegrated Design flow for Reconfigurable Architectures. The key part of INDRA 2.0 is DHHarMa: a Design flow for Homogeneous Hard Macros, which generates homogeneous hard macros for Xilinx FPGAs starting from a high-level description (e.g., VHDL). In particular, the homogeneous DHHarMa router is explained in detail, providing novel terminologies and algorithms, which have enabled the generation of homogeneous routed designs. Results have been shown that Design flow for Homogeneous Hard Macros (DHHarMa) can route homogeneously a communication infrastructure utilizing just between 1% and 31% more resources than the Xilinx router, which cannot provide a homogeneous solution.

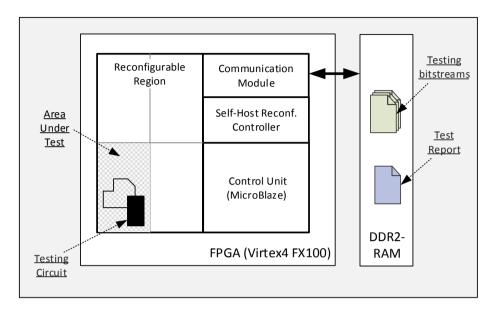

Furthermore, the permanent faults that can occur on FPGAs have been investigated. This thesis presents OLT(RE)<sup>2</sup>: an on-line on-demand approach to testing permanent faults induced by radiation in reconfigurable systems used in space missions. The proposed approach relies on a test circuit and custom placer and router. OLT(RE)<sup>2</sup> exploits DPR to place the test circuits at run-time. Its goal is to test unprogrammed areas of the FPGA before using them. Experimental results of OLT(RE)<sup>2</sup> have shown that is possible to generate, place, and route the test circuits needed to detect on average more than 99 % of the physical wires and on average about 97 % of the programmable interconnection points of a large arbitrary region of the FPGA in a reasonable time. Moreover, the test can be run on the target device without interfering the functional behavior of the system.

# **Contents**

| 1 | Intro | oductio  | on                                                          | 1  |

|---|-------|----------|-------------------------------------------------------------|----|

|   | 1.1   | Dynai    | mic Reconfigurable Processing Module                        | 2  |

|   | 1.2   | INteg    | rated Design flow for Reconfigurable Architectures 2.0      | 2  |

|   | 1.3   |          | ne Testing of Permanent Radiation Effects in Reconfigurable |    |

|   |       | Syster   | m                                                           | 3  |

|   | 1.4   | Orgar    | nization                                                    | 4  |

| 2 | Bac   | kgrour   | nd                                                          | 7  |

|   | 2.1   | SRAN     | 1-based FPGA Architecture                                   | 8  |

|   |       | 2.1.1    | Terminology                                                 | 10 |

|   |       | 2.1.2    | Clock Regions                                               | 11 |

|   |       | 2.1.3    | Programmable Interconnection Points (PIPs)                  | 11 |

|   |       | 2.1.4    | Configuration Memory (Bitstream)                            | 12 |

|   |       | 2.1.5    | Routing Physical Wires                                      | 14 |

|   |       | 2.1.6    | Xilinx FPGA families                                        | 16 |

|   |       | 2.1.7    | Space-Grade devices                                         | 22 |

|   | 2.2   | Dynai    | mic Partial Reconfiguration                                 | 24 |

|   |       | 2.2.1    | Benefits                                                    | 25 |

|   |       | 2.2.2    | FPGA partitioning                                           | 26 |

|   |       | 2.2.3    | Communication Infrastructure in a PR system                 | 27 |

|   |       | 2.2.4    | Embedded Macros                                             | 30 |

|   | 2.3   | Xilinx   | Design Flow                                                 | 31 |

|   |       | 2.3.1    | ISE                                                         | 31 |

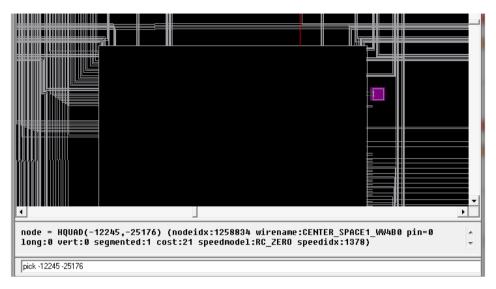

|   |       | 2.3.2    | FPGA Editor                                                 | 33 |

|   |       | 2.3.3    | XDL tool                                                    | 34 |

|   |       | 2.3.4    | Vivado                                                      | 36 |

|   | 2.4   | Radia    | tion Effects                                                | 37 |

|   |       | 2.4.1    | Single Event Effects                                        | 38 |

|   |       | 2.4.2    | Total Ionizing Dose                                         | 39 |

|   |       | 2.4.3    | Radiation Sensitiveness on SRAM-based FPGAs                 | 40 |

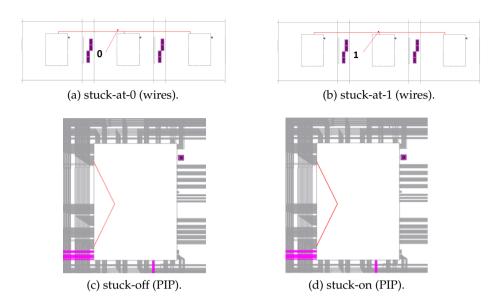

|   |       | 2.4.4    | Permanent Faults in Routing Resources                       | 42 |

| 3 | Stat  | te of th | e Art                                                       | 47 |

|   | 3.1   | XDL-l    | based databases and APIs                                    | 47 |

|   |       | 3.1.1    | ReCoBus and GoAhead                                         | 48 |

|     | 3.1.2          | RapidSmith                                         | 48        |

|-----|----------------|----------------------------------------------------|-----------|

|     | 3.1.3          |                                                    | 19        |

|     | 3.1.4          | Tincr                                              | 19        |

|     | 3.1.5          | Comparison                                         | 50        |

| 3.2 | Dynai          |                                                    | 51        |

|     | 3.2.1          | Xilinx ISE Dynamic Partial Reconfiguration (DPR) 5 | 52        |

|     | 3.2.2          |                                                    | 54        |

|     | 3.2.3          | ReCoBus and GoAhead                                | 55        |

|     | 3.2.4          | OpenPR                                             | 55        |

|     | 3.2.5          | Dreams                                             | 56        |

|     | 3.2.6          |                                                    | 57        |

| 3.3 | Recon          | ofiguration in Space Applications                  | 58        |

|     | 3.3.1          | DPR research platforms                             | 59        |

|     | 3.3.2          | In-flight reconfigurable space-missions 6          | 60        |

|     | 3.3.3          | Commercial FPGAs in Space                          | 52        |

|     | 3.3.4          | Comparison                                         | 53        |

| 3.4 | Testin         | g of Routing Resources                             | 54        |

|     | 3.4.1          |                                                    | 55        |

|     | 3.4.2          |                                                    | 66        |

|     | 3.4.3          |                                                    | 67        |

|     | 3.4.4          |                                                    | 58        |

| 3.5 | Sumn           | nary                                               | 59        |

|     |                | Use Description makely Durance in a Mandala.       |           |

| _   |                | , ,                                                | 71<br>71  |

| 4.1 | 2              |                                                    | 71<br>73  |

|     | 4.1.1          |                                                    | / 3<br>74 |

|     | 4.1.2          |                                                    |           |

|     | 4.1.3          |                                                    | 76        |

| 4.0 | 4.1.4          |                                                    | 76        |

| 4.2 | 4.2.1          | 0 \ /                                              | 77<br>78  |

| 4.3 |                |                                                    | 79        |

| 4.3 | 4.3.1          |                                                    | 79<br>30  |

|     | 4.3.1          |                                                    | 31        |

|     | 4.3.3          |                                                    | 31<br>32  |

|     |                |                                                    |           |

|     | 4.3.4<br>4.3.5 |                                                    | 34        |

|     |                |                                                    | 36<br>37  |

|     | 4.3.6          |                                                    |           |

|     | 4.3.7          | 1                                                  | 90        |

| 1 1 | 4.3.8          | J                                                  | 91        |

| 4.4 |                |                                                    | 92<br>92  |

|     | 4.4.1          | AVIOLIC INTELLIGES LESTING                         | jΖ        |

4

|   |     |         | DRPM GUI                                                   |     |

|---|-----|---------|------------------------------------------------------------|-----|

|   | 4.5 | Summ    | nary                                                       | 96  |

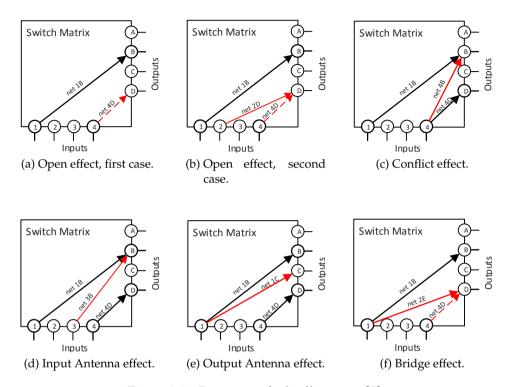

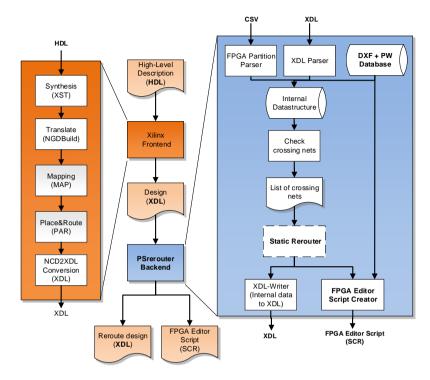

| 5 | IND | RA 2.0  |                                                            | 97  |

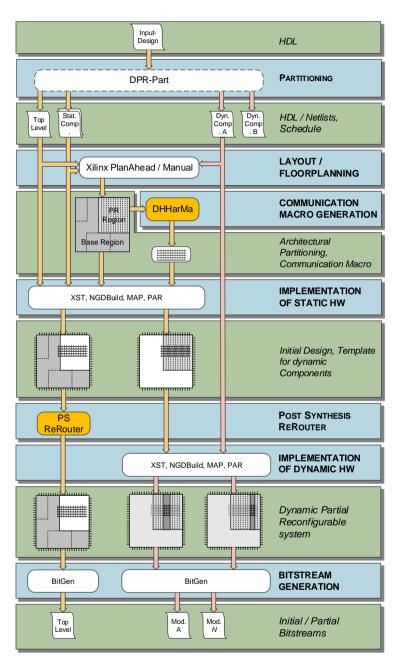

|   | 5.1 | Flow I  | Description                                                | 97  |

|   |     | 5.1.1   | FPGA partitioning                                          |     |

|   |     | 5.1.2   | Communication Macro Generation (DHHarMa)                   | 98  |

|   |     | 5.1.3   | Static PAR and PSRerouter                                  | 100 |

|   |     | 5.1.4   | Dynamic Modules Implementation                             | 100 |

|   |     | 5.1.5   | Bitstream Generation                                       |     |

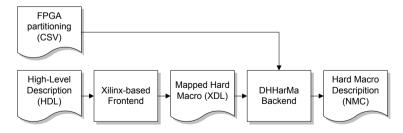

|   | 5.2 | Design  | n flow for Homogeneous Hard Macros                         | 101 |

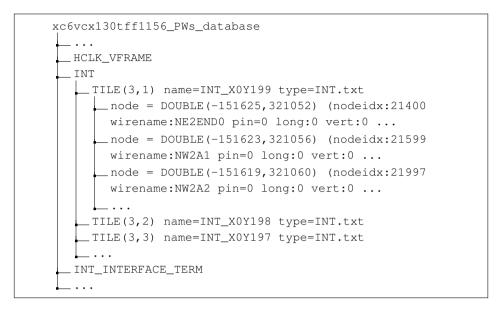

|   |     | 5.2.1   | Datastructure for Xilinx FPGAs (DXF)                       | 102 |

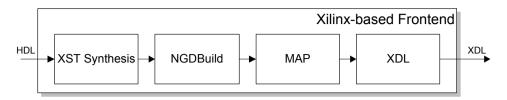

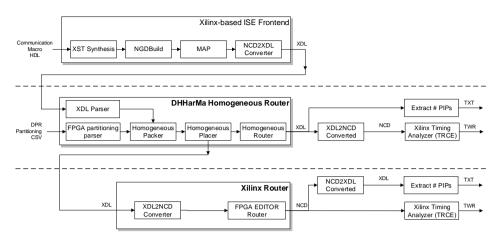

|   |     | 5.2.2   | Xilinx-based front-end                                     | 103 |

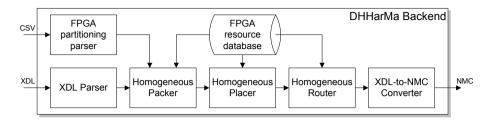

|   |     | 5.2.3   | DHHarMa back-end                                           | 104 |

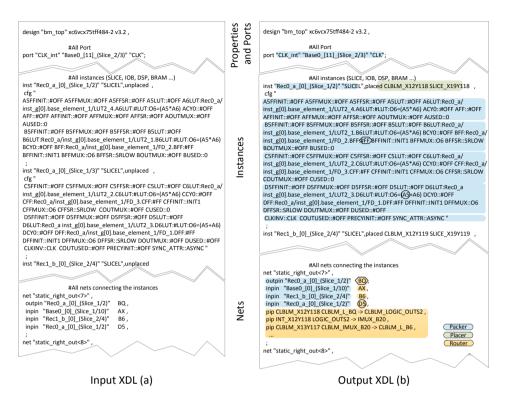

|   |     | 5.2.4   | Output XDL File                                            | 105 |

|   | 5.3 | PSRer   | outer                                                      | 106 |

|   |     | 5.3.1   | Problem definition                                         | 108 |

|   |     | 5.3.2   | Implementation Idea                                        | 109 |

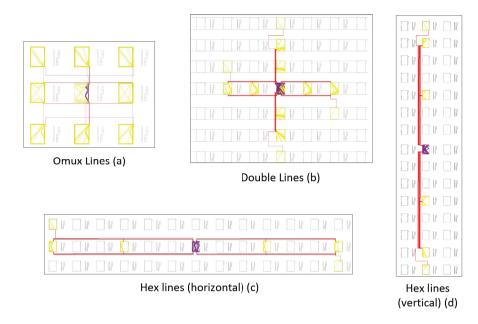

|   |     | 5.3.3   | Physical Wire Info                                         | 110 |

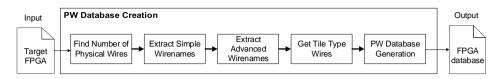

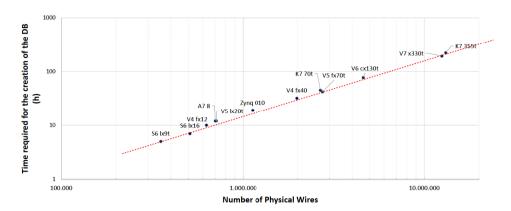

|   |     | 5.3.4   | Database Creation Flow                                     | 112 |

|   |     | 5.3.5   | Benchmark                                                  | 118 |

|   |     | 5.3.6   | Post-Synthesis Rerouter (PSRerouter) flow                  | 119 |

|   | 5.4 | Summ    | nary                                                       | 123 |

| 6 | DHF | larMa I | Router                                                     | 125 |

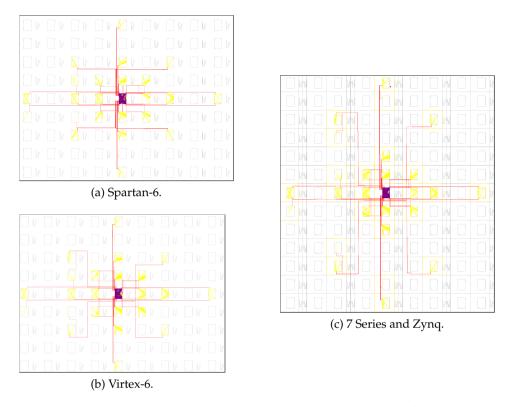

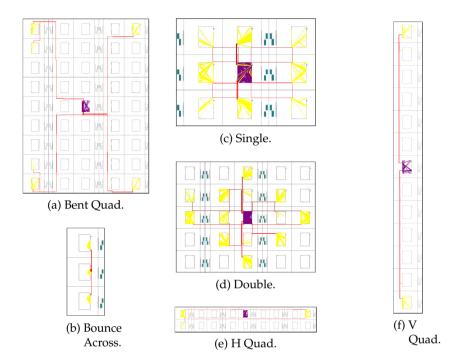

|   | 6.1 |         | al Purpose Routing Analysis                                |     |

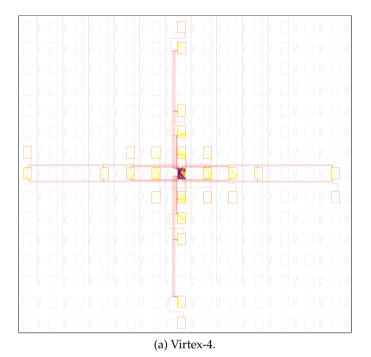

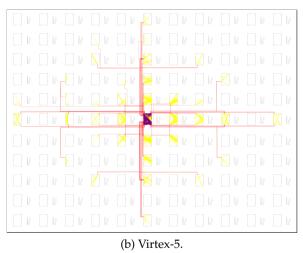

|   |     | 6.1.1   | Virtex-4                                                   |     |

|   |     | 6.1.2   | Virtex-5                                                   |     |

|   |     | 6.1.3   | Virtex-6 and Spartan-6                                     |     |

|   |     | 6.1.4   | 7 Series and Zynq                                          |     |

|   | 6.2 | Homo    | ogeneous Routing Base Concepts                             |     |

|   |     | 6.2.1   | Standard Routing Algorithms                                |     |

|   |     | 6.2.2   | Iterative Deepening Depth-First Search algorithm (IDDFS) . |     |

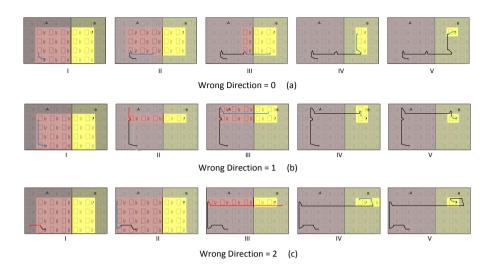

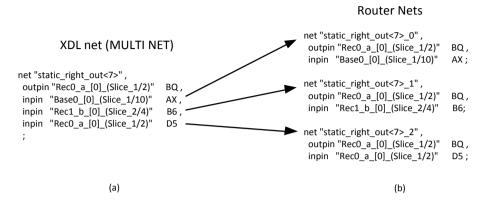

|   |     | 6.2.3   | Routing Direction and Wrong Direction                      |     |

|   |     | 6.2.4   | Nets Terminology                                           |     |

|   |     | 6.2.5   | Net Initialization                                         |     |

|   |     | 6.2.6   | Master and Slave Regions                                   | 138 |

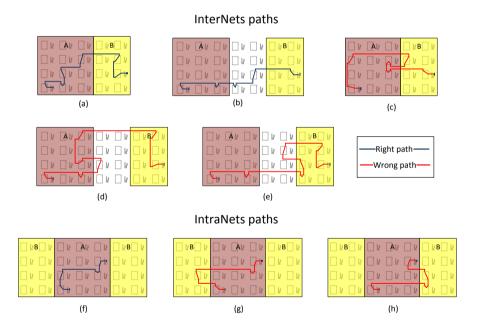

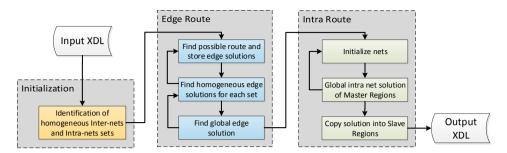

|   | 6.3 | DHHa    | arMa Homogeneous Router Flow                               |     |

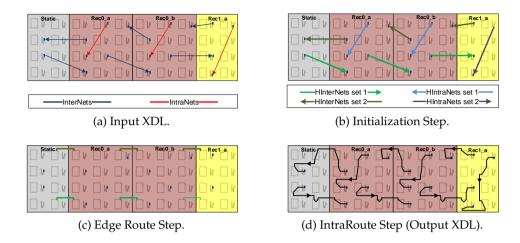

|   |     | 6.3.1   | Initialization Phase                                       | 139 |

|   |     | 6.3.2   | Edge Routing Phase                                         |     |

|   |     | 6.3.3   | Intra-Routing Phase                                        |     |

|     | 6.4   | DHH               | arMa Results                                              | 146 |

|-----|-------|-------------------|-----------------------------------------------------------|-----|

|     |       | 6.4.1             | Routing Experiment Flow                                   | 146 |

|     |       | 6.4.2             | Routing comparison                                        | 147 |

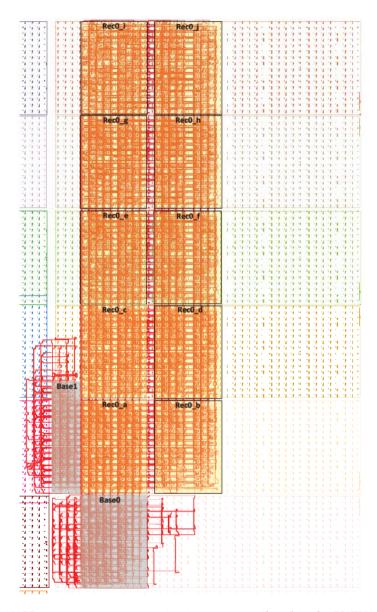

|     |       | 6.4.3             | DRPM communication infrastructure                         | 150 |

|     |       | 6.4.4             | Further Applications of the Homogeneous Router            | 151 |

|     | 6.5   | Sumn              | nary                                                      | 154 |

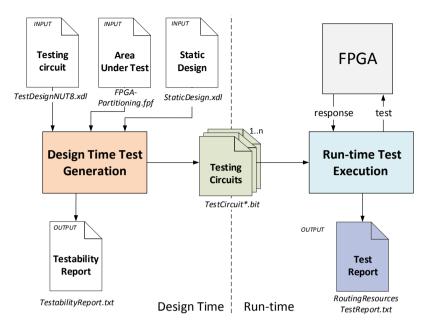

| 7   | OLT   | (RE) <sup>2</sup> |                                                           | 155 |

|     | 7.1   | ` '               | Structure                                                 | 156 |

|     |       | 7.1.1             | The On-Line Testing of Permanent Radiation Effects in Re- |     |

|     |       |                   | configurable System (OLT(RE) <sup>2</sup> ) CAD Flow      | 157 |

|     |       | 7.1.2             | Design-time Test Generation Sub-flow                      |     |

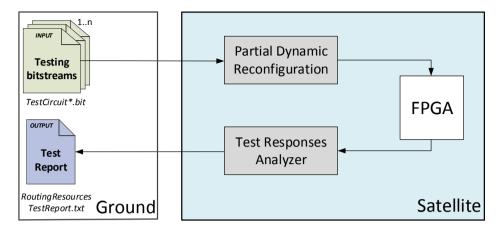

|     |       | 7.1.3             | Run-time Test Execution Sub-flow                          |     |

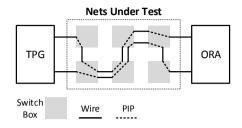

|     | 7.2   | Circui            | its for Testing of Permanent Faults                       |     |

|     |       | 7.2.1             | The 8-NUT Hard-Macro                                      |     |

|     |       | 7.2.2             | Routing Faults Test Principles                            |     |

|     | 7.3   | Graph             | n Model of FPGA                                           |     |

|     |       | 7.3.1             | Stuck-at Coverage                                         | 164 |

|     |       | 7.3.2             | Stuck-off Coverage                                        |     |

|     |       | 7.3.3             | Stuck-on Coverage                                         | 165 |

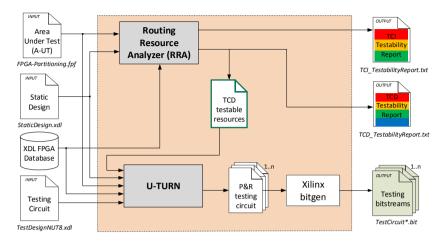

|     | 7.4   | Routi             | ng Resources Analyzer                                     | 167 |

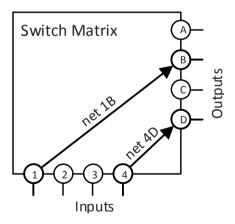

|     |       | 7.4.1             | Testability of the Routing Resources                      | 167 |

|     |       | 7.4.2             | Routing Resources Analyzer Flow                           | 170 |

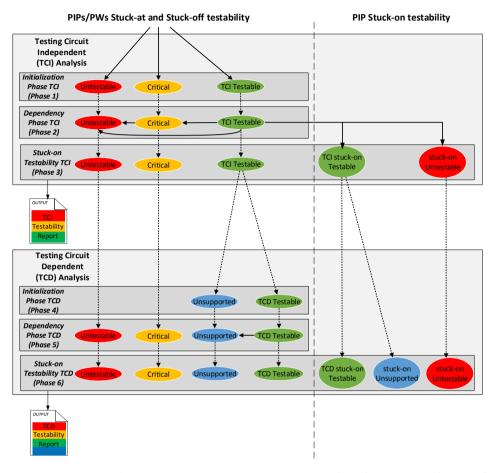

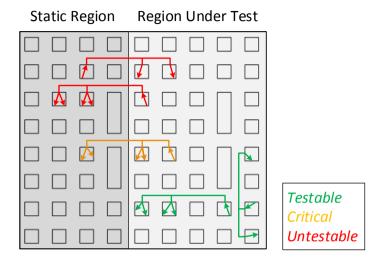

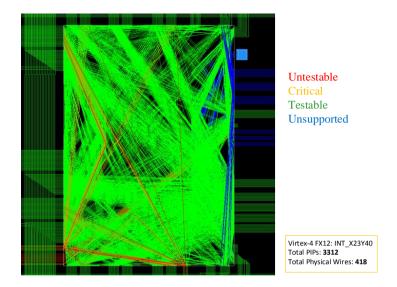

|     |       | 7.4.3             | Testing Circuit Independent (TCI) Analysis                | 170 |

|     |       | 7.4.4             | Testing Circuit Dependent (TCD) Analysis                  | 174 |

|     |       | 7.4.5             | Result Output                                             | 175 |

|     | 7.5   | The U             | I-TURN Place-and-Route Algorithm                          | 179 |

|     |       | 7.5.1             | The TPG & ORA Placer                                      | 179 |

|     |       | 7.5.2             | The Net Under Tests (N-UTs) Router                        | 181 |

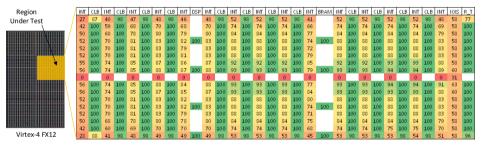

|     | 7.6   | Resul             |                                                           |     |

|     |       | 7.6.1             | Test Circuit Validation                                   |     |

|     |       | 7.6.2             | Design-time Performance Analysis                          |     |

|     |       | 7.6.3             | Run-time Performance Analysis                             |     |

|     | 7.7   | Sumn              | nary                                                      | 190 |

| В   | Con   | clusio            | n and Outlook                                             | 191 |

|     | 8.1   | Outlo             | ok                                                        | 192 |

| Li  | st of | Figure            | s                                                         | 195 |

| l i | st of | Tahles            |                                                           | 199 |

| Acronyms              | 201 |

|-----------------------|-----|

| Bibliography          | 207 |

| Advised Thesis        | 223 |

| Author's Publications | 225 |

# 1 Introduction

Reconfigurable architectures have become key implementation platforms for digital circuits in many application areas. Although Field Programmable Gate Arrays (FPGAs) progressively changed from homogeneous architectures containing identical logic cells to heterogeneous architectures containing different types of cells (e.g., Configurable Logic Block (CLB), Block Random Access Memory (Block RAM), Digital Signal Processor (DSP)), the structure itself is still regular and homogeneous.

The regularity of resources within an FPGAs is a remarkable feature, which is utilized in timing critical application domains; an example is a time-to-digital converter where the regularity of the routing structure is exploited to time difference measurement between two pulses. Dynamic Partial Reconfiguration (DPR) is another application domain, where the regularity of the FPGA resources is exploited; a hardware module that is placed in a specific area can be relocated in a different one, which has the same resources of the starting area. Thus, the regularity of the partially reconfigurable region increases the flexibility of the hardware modules placement.

Reconfigurable hardware has also gained a steadily growing interest in the domain of *space applications*. The reconfiguration of the hardware at run-time combined with the high computational power of modern FPGAs turn these devices interesting candidate for data processing in space applications. The DPR of FPGAs allows flexibility and can increase performance, improve energy efficiency, and enhance fault tolerance. The utilization of DPR on Commercial Off-the-Shelf (COTS) Xilinx FPGAs in space application is investigated in this thesis. A prototyping platform, novel tools, and fault mitigation mechanisms are provided.

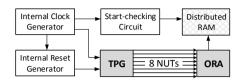

The main parts of the thesis are: Dynamic Reconfigurable Processing Module (DRPM) platform that gives the possibility to exploit DPR in space applications; INtegrated Design flow for Reconfigurable Architectures 2.0 (INDRA 2.0) framework that enables the creation of DPR scenarios, which support the relocation of hardware module; On-Line Testing of Permanent Radiation Effects in Reconfigurable System (OLT(RE)<sup>2</sup>) tool that generates testing circuits, which can detect on-line permanent faults on an FPGA.

# 1.1 Dynamic Reconfigurable Processing Module

Dynamic Reconfigurable Processing Module (DRPM) is a demonstrator that aims to exploit run-time adaptability and high-performance of payload processing systems, which is capable of exploiting DPR on SRAM-based FPGAs in space mission scenarios. The platform also embeds advanced tools and methods that mitigate radiation effects (e.g., Single Event Upset (SEU) and Total Ionizing Dose (TID)).

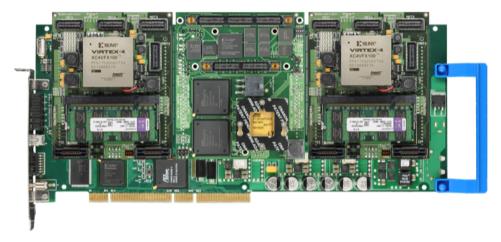

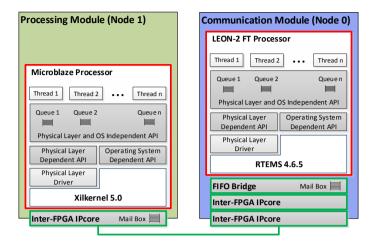

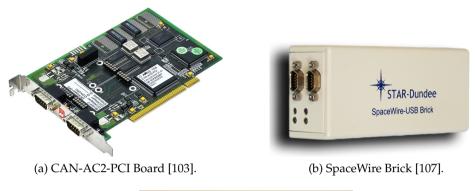

Thanks to DPR, blind and readback scrubbing are supported; the scrubbing rate can be adapted individually to different parts of the design. The demonstrator is based on the *RAPTOR-X64* prototyping environment, developed by the *Cognitronics and Sensor Systems* at *Bielefeld University*. DRPM combines dynamically reconfigurable FPGAs with avionic interfaces (e.g., SpaceWire, MIL-STD-1553B, and SpaceFibre).

The thesis provides information regarding the software infrastructure of the DRPM. Moreover, this work introduces a novel general-purpose multiprocessor communication protocol, which allows a fast and reliable communication among different processors of the system: the Heterogeneous Multi Processor Communication Interface (HMPCI). Furthermore, the DRPM proves the presented CAD tools INDRA 2.0 and OLT(RE)<sup>2</sup>. The DRPM is a European Space Agency (ESA) funded TRP project (22424/09/NL/LvH) [37] and has been developed by the *Cognitronics and Sensor Systems* at *Bielefeld University* in collaboration with *Swiss Space Technology*, *TWT GmbH Science & Innovation*, and *Politecnico di Torino*.

# 1.2 INtegrated Design flow for Reconfigurable Architectures 2.0

Commercial FPGA tools do not allow exploiting all the DPR capabilities. For example, they are unable to create DPR systems that support the relocation of Partial Reconfigurable Modules (PR Modules). Therefore, this thesis introduces a new DPR flow: *INtegrated Design flow for Reconfigurable Architectures 2.0 (INDRA 2.0)*. This flow provides novel functionalities that enable the creation of a custom and advanced DPR scenarios in modern FPGAs. The key parts of this novel flow are the *Design flow for Homogeneous Hard Macros (DHHarMa)* and the *Post-Synthesis Rerouter (PSRerouter)*.

DHHarMa automatically generates homogeneous hard macros for Xilinx FPGAs starting from a high-level description, such as Very High Speed Integrated Circuit Hardware Description Language (VHDL) or Verilog HDL. Starting from HDL gives the designer the ability to quickly create and modify designs, which require being homogeneously placed and routed. The core components of DHHarMa are

a homogeneous packer, placer, and router, which generate a regular structured design, based on a user-defined FPGA partitioning. This thesis presents the homogeneous routing phase.

PSRerouter is a tool of INDRA 2.0. It can reroute nets of a design after the synthesis process. This operation is needed because vendor's Place and Route (PAR) tools do not permit inserting specific constraints on the routing policy. Therefore, PSRerouter enables to reroute specific nets of a design, allowing the creation of DPR systems that ensure Partial Reconfigurable Module (PR Module) relocation.

DHHarMa and PSRerouter rely on a custom database containing the complete description of the resources of a given FPGA: *Datastructure for Xilinx FPGAs (DXF)*. It has been created from the Xilinx *XDLRC* report and *FPGA-Edline* scripting language. This database allows having a deep interaction with the Xilinx commercial tools (e.g., Integrated Software Environment (ISE) and FPGA Editor). These tools are suitable for a wide number of Xilinx FPGAs: Virtex-4, Virtex-5, Virtex-6, Spartan-6, 7 Series (i.e., Artix-7, Kintex-7, and Virtex-7), and Zynq.

# 1.3 On-Line Testing of Permanent Radiation Effects in Reconfigurable System

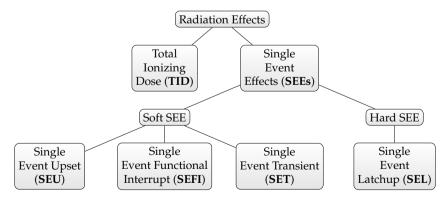

OLT(RE)<sup>2</sup> is a software flow for the generation of hard macros for on-line testing and diagnosing of permanent faults due to radiation in SRAM-based FPGAs used in space missions. Radiations in the atmosphere may damage electronic devices employed in space systems. In particular, radiations may induce both instantaneous and long-term damages. Instantaneous damages are typically *SEUs* (i.e., modifications of the content of memory elements in the device) and Single Event Transition (SET) (i.e., transient undesired electrical impulses). Differently, the long-term damages induced by radiations are caused by *TID*, i.e., the accumulation of charge trapped in the oxide layer of transistors in CMOS circuits.

In the last decade, many works focused SEUs, which are soft errors that can occur in space missions. Nevertheless, permanent faults (e.g., caused by TIDs) need to be considered in present/future reconfigurable systems designed for space missions. OLT(RE)<sup>2</sup> connects ideas and background from different inventors that aimed mitigation and detection of SEU effects to detect permanent faults caused by TID as well. The test approach of OLT(RE)<sup>2</sup> exploits the DPR mechanism provided by modern SRAM-based FPGAs.

The testing technique is meant to be applied on-line and on-demand to detect permanent faults in reconfigurable systems. On the one hand, it can help designers in making use of high-performance unreliable COTS FPGAs viable for space applications; on the other hand, it can help the increase of low-cost application scenarios systems where high-end radiation-hardened devices are not affordable. The presented approach is compatible with a wide number of Xilinx FPGAs: Virtex-4, Virtex-5, Virtex-6, and Spartan-6. Moreover, the flow has been validated on the DRPM platform. OLT(RE)<sup>2</sup> has been partially funded by *European Space Agency (ESA)* and developed by the *Cognitronics and Sensor Systems Group* at *Bielefeld University*, in collaboration with *Pisa University* and *Politecnico di Torino*.

# 1.4 Organization

Chapter 2 provides the needed background concepts of the presented thesis work. The Xilinx FPGA architecture is introduced, by providing terminology and details of the different FPGA families. A description of the DPR mechanism is given, which is a concept strongly used in all the aspects of this thesis. Successively, the radiation effects on FPGAs are presented, giving information regarding the possible errors that can be induced in the routing structure. Finally, since the thesis provides new tools that can be utilized with the vendor ones, the Xilinx tools are presented, focusing on their properties and integration methods.

Chapter 3 presents the state of the art of this thesis. First, it is explained why the Xilinx tools do not allow exploiting DPR capability of the FPGAs completely; then, related works are investigated as well. Moreover, the DRPM motivations are presented, highlighting the novel features that this new platform introduces compared to the current reconfigurable platforms. Finally, testing of FPGAs background is provided, focusing on the leak of on-line testing of FPGAs in space applications.

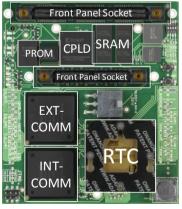

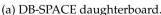

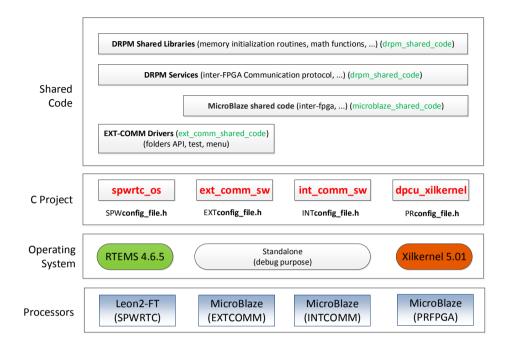

Chapter 4 describes the DRPM platform, focusing on its hardware and software properties. The base platform (*RAPTOR-X64*) and the modular boards (*DB-V4* and *DB-SPACE*) are presented. Moreover, a deep description of its inter-processors communication protocol called *Heterogeneous Multi Processor Communication Interface* (*HMPCI*) is provided. Finally, the DRPM GUI is presented, which allows configuring and validating the overall platform.

Chapter 5 presents INDRA 2.0. This flow allows exploiting the full capability of DPR into modern Xilinx FPGAs. The flow supports the integration with the official Xilinx tools. Specifically, INDRA 2.0 enables to create scenarios in which reconfigurable modules can be relocated; the flow relies on a custom *Datastructure for Xilinx FPGAs (DXF)* created with the XDL-reports, which contains the structure information of the FPGAs. A special Rerouter tool has been implemented, which allows unrouting/routing specific design nets to enable module relocation.

Chapter 6 provides a detailed description of DHHarMa. Its key parts (i.e., Homogeneous Packer, Homogeneous Placer and Homogeneous Router) are presented. It gives an extensive explanation of the Homogeneous Router parts, considering the novel concepts that allow generating a homogeneous routed design. Moreover,

it provides an analysis of the routing structure of different Xilinx FPGA families. Finally, case studies and results are discussed.

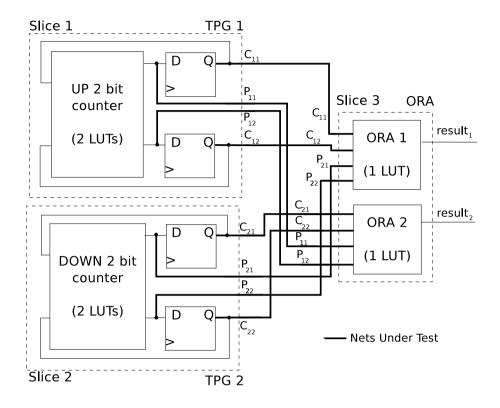

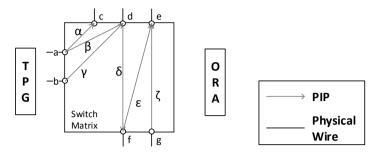

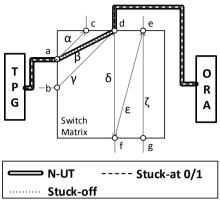

Chapter 7 presents OLT(RE)<sup>2</sup>. First, the flow and its innovation in on-line testing are discussed. Then, a dedicated testing circuit is explained, which permits performing the on-board test on an FPGA device. The chapter also introduces new concepts and solutions to categorize the different FPGA's routing resources. Furthermore, a detailed explanation of the PAR algorithm (*U-TURN*) is provided. Finally, the performance and the test coverage of the testing approach on different devices is considered.

# 2 Background

Field-Programmable Gate Arrays (FPGAs) are prefabricated silicon devices that can be electrically programmed to become almost any kind of digital circuit or system [15; 91]. Initially, these devices provided simple logic functions. Nowadays, FPGAs can implement complex systems in one chip; hence, they are used in a growing number of applications [38]. The biggest available FPGA, the Xilinx Virtex UltraScale VU440, integrates 5.5 M logic blocks and 2,880 DSP blocks [140].

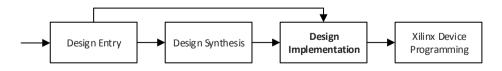

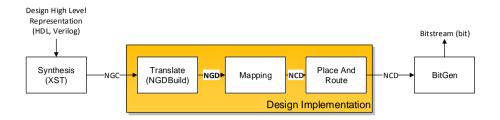

In contrast to Application Specific Integrated Circuits (ASICs), which are designed for specific applications, FPGAs are configured after their fabrication. Furthermore, they can be reconfigured multiple times. The configuration is done starting from a hardware description language (HDL) of a certain digital circuit, which is compiled to a bitstream and downloaded to the FPGA.

One of the main advantages of using FPGAs is the decreasing time-to-market required for an application. FPGAs allow designers to concentrate on the development of applications, without focusing on the device fabrication problems. Moreover, the target device of an application is already available since the beginning of the development phase.

On the contrary, when the target implementation is an ASIC, the device is available just at the end of the fabrication process. For these reasons, ASIC implementation is usually advantageous when a large scale production is planned. Therefore, FPGAs can be a much cheaper and faster solution, when a specific and small-scale task is required.

SRAM-based FPGAs allow designers to reuse and reconfigure a device several times; hence, reconfigurability gives different remarkable advantages, such as:

- **Testing**: FPGAs can be utilized as prototype platforms [59], allowing a deeper and faster validation of an application (compared to the simulation software).

- Application Update: the use of a reprogrammable device can extend the lifetime of a product. Nowadays, algorithms and standards are chaining fast (e.g., video decoding algorithms, communication protocols); updating an algorithm can allow using a product longer and more efficiently.

- **Time-share Applications**: to reduce cost and space of a device, different tasks can be programmed into a single device, at various instance of time.

Partial-Reconfiguration: some SRAM-based devices offer the property to reconfigure just parts of an FPGA. In particular, during a partial reconfiguration, the non-reconfigured part can still operate without being interrupted.

FPGAs are utilized in space missions as well. In this field, the final application has specific targets and a limited number of exemplars; the cost of implementing an ASIC for each new satellite can turn in a higher final cost. Thereby, FPGAs are extraordinary increasing in space market; furthermore, they can offer all the advantages of device reprogrammability (as describe above).

However, due to the harsh-environment they operate in, FPGAs have to respect special requirements and be fault tolerant to radiations. Differently from a ground application, a critical fault on space applications cannot be solved by analyzing the components with a typical repairing process (e.g., unmount the device, exchange a broken part, execute off-line tests).

In the following, the organization of the chapter is presented. Section 2.1 provides the FPGA's background information to understand the implementation part of this thesis (i.e., FPGA architecture, different Xilinx devices, Dynamic Partial Reconfiguration). Section 2.2 focuses on DPR, introducing important concepts, such as FPGA partitioning and communication infrastructures for reconfigurable systems. Section 2.4 introduces the space harsh-environment, analyzing temporary and permanent faults effects that radiations can cause. Then, the radiation effects on SRAM-based FPGAs are considered, focusing on the routing resources effects of a fault (e.g., antenna, open). Finally, Section 2.3 presents the Xilinx ISE software design flow, highlighting the parts that are mostly used in this thesis.

### 2.1 SRAM-based FPGA Architecture

FPGAs are mainly divided into three categories: the first, *antifuse FPGAs*, consists of electronically programmable configuration memories that can be programmed only once; the second, flash-based FPGAs, consist of devices which are configured with flash configuration memory; the third, *SRAM-based FPGAs*, comprises devices that are based on a Static Random Access Memory (SRAM) configuration memory, which controls the FPGA configuration. Hence, SRAM-based FPGAs can be programmed multiple times [5]. When FPGAs were introduced in the 80s, antifuse devices were preferred, thanks to their greater stability compared to the first SRAM-based models. However, in the next years, the SRAM memories became more stable, allowing a fast spreading of SRAM-based FPGAs.

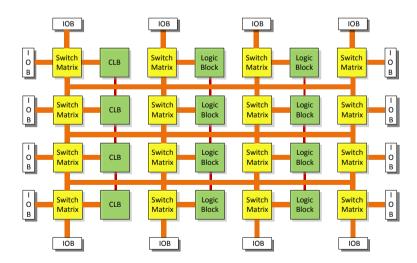

Antifuse, SRAM-based, and flash-based FPGAs have the same high-level architecture, which consists mainly of three components: Logic Blocks, Interconnection matrices (INTs) and Input Output Blocks (IOBs). Figure 2.1 shows how these components are interconnected.

In the following, the FPGA's components are presented:

- Logic Blocks: are the main logical resources that implement sequential and combinatorial circuits; Xilinx calls them Configurable Logic Blocks (CLBs). The structure of a CLB is hierarchically divided into logical cells (called slices) that contain Look Up Tables (LUTs). In FPGAs of different manufacturers, the number of logical cells within a Logic Block can differ; in current Xilinx FPGAs, the number of slices can be either 2 or 4 according to the FPGA family.

- *Input Output Blocks (IOBs)*: provide outside connections of the FPGA. These blocks are generally placed at the borders of the FPGA, and they are used to getting the signals into and outwards the FPGA.

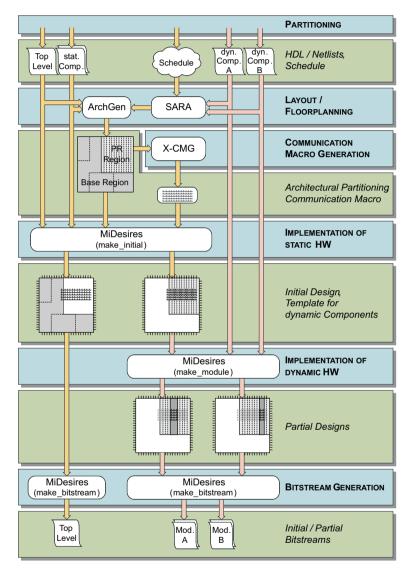

- Interconnection matrices (INTs): all the FPGA logic blocks are connected among them with a complex general routing structure. With an INT, also called switch matrix, it is possible to drive signals within the FPGA (e.g., connect two different CLB blocks). The routing is provided activating the Programmable Interconnection Points (PIPs), which are located within the switch matrix. All INTs are connected among them utilizing a complex structure of fixed connections, which is presented in detailed in Section 2.1.5 and Section 6.1.

Figure 2.1: The general architecture of a Xilinx FPGA.

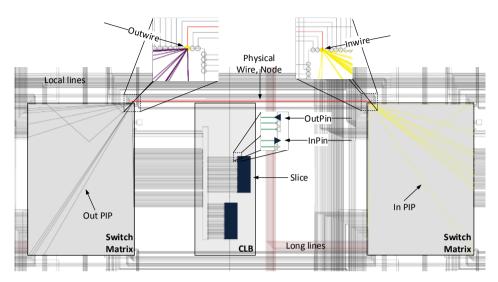

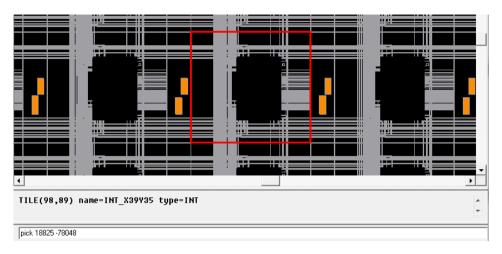

Figure 2.2: A summary of the FPGA resources terminology. A screenshot of FPGA Editor [128] has been utilized.

#### 2.1.1 Terminology

This thesis focuses on the low-level architecture of the FPGA. In the following, basic terminologies and concepts are provided, which are extensively used in the rest of the thesis. It is worth to mention that these terminologies are strongly related to Xilinx FPGAs, which are the target devices for this work.

Figure 2.2 shows a screenshot of a Xilinx FPGA taken from the FPGA Editor tool (presented in Section 2.3.2). The screenshot shows a portion of an FPGA, highlighting the main components considered in this works; according to the depicted in Figure 2.1, this picture shows a CLB, two INTs, and physical connections lines.

This supports the following terminology:

- *Slice*: the basic logic building block of an FPGA. A slice includes the configurable resources for the implementation of Boolean functions, as well as flip-flops and carry propagation logic.

- *Physical wire* (*PW*): a hard-wired non-configurable interconnection between either two switch matrices or a CLB and a switch matrix.

- *Pin*: a connection point between a slice and a physical wire (PW). In case the direction of the signal goes into the slice, the Pin is called *inPin*; *outPin* otherwise.

|                    | Virtex-4 | Virtex-5 | Spartan-6 | Virtex-6 | 7 Series, |

|--------------------|----------|----------|-----------|----------|-----------|

|                    |          |          | 1         |          | Zynq      |

|                    | [145]    | [148]    | [138]     | [150]    | [122]     |

| Number of CRs      | 8-24     | 6-24     | 8-24      | 6-18     | 4-24      |

| Height of a CR     | 16 CLB   | 20 CLB   | 16 CLB    | 40 CLB   | 50 CLB    |

| Clocks within a CR | 8        | 10       | 16        | 12       | 12        |

Table 2.1: Clock Region (CR) properties of Xilinx FPGAs.

- *Wire*: a connection point between a PW and a switch matrix. In case the signal direction goes into the INT, the Wire is called *inWire*; *outWire* otherwise.

- Programmable Interconnection Point (PIP): a configurable connection between

two wires belonging to the same INT. It is worth noting that multiple PIPs

are connected to the same inWire as well as multiple PIPs are attached to the

same outWire. PIPs are discussed in Section 2.1.3.

#### 2.1.2 Clock Regions

For clocking distribution purpose, Xilinx FPGAs are partitioned into *clock regions*. Clock regions are the fundamental parts of an FPGA, which allow low clock skew (i.e., unsynchronized distribution of the clock cycles) across the device. The number of clock regions varies from device to device. However, all the considered Xilinx FPGAs are partitioned in a matrix of clock regions, which always have two columns (a clock region spans in all the cases half of the die). Moreover, for each FPGAs family, a clock region has always fix high.

Table 2.1 shows how the number and dimension of a clock region change according to a certain device. The height of a clock region goes from 16 CLB in the Virtex-4 to 50 CLB in the 7 Series and Zynq (these two families have the same FPGA architecture). The different Xilinx FPGA families are presented in Section 2.1.6. On the contrary, the number of clock regions is almost the same in newer devices. It is worth to mention that a column of a clock region is called *frame*. A frame is the smallest addressable element of the Xilinx FPGA bitstream (see Section 2.1.4).

## 2.1.3 Programmable Interconnection Points (PIPs)

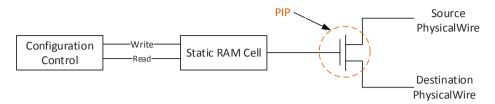

The PIPs are programmable CMOS transistors that allow a certain signal to be routed into the device (Figure 2.3) [64]. The logic blocks inside an FPGA communicate among them utilizing a complex structure of fixed connections (see Section 6.1). It is possible to route a signal over this routing network activating PIPs.

Figure 2.3: Programmable Interconnection Point (PIP) representation.

More in detail, the SRAM technology has five transistors that form the SRAM cell and a pass transistor that creates the contacts [32; 64]. Thereby, PIP transmits a signal depending on the value in its configuration memory cell. The PIP concept is extensively utilized within all the presented work, considering their utilization and testing. The number of PIPs can vary according to the device dimension and Virtex FPGAs.

#### 2.1.4 Configuration Memory (Bitstream)

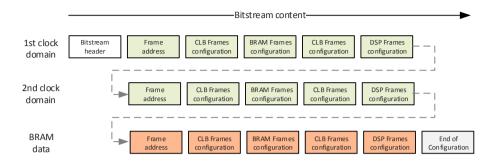

The configuration memory is the part that controls the overall configuration of an SRAM-based FPGA. The information stored in the configuration memory is called *bitstream*. The FPGA families considered in this work have a slightly different organization of their configuration bitstreams; however, the general structure is the same.

The bitstream is composed of a set of *frames*. A frame corresponds to an FPGA clock region column, and it spans vertically from the top to the bottom of the configuration memory. Moreover, a frame is the atomic part of the bitstream that can be configured. When a frame is transferred into the device, a final state machine takes care of transferring the data in the correct position of the configuration memory.

For every FPGA family, Xilinx provides guides regarding its configuration memory [123; 139; 142; 147; 151]. The documents give details and information regarding the configuration interfaces (i.e., Serial, SelectMap, Master Serial Peripheral Interface (SPI), Master Byte-wide Peripheral Interface (BPI) and Joint Test Action Group (JTAG) configuration interface), dynamic reconfiguration ports and bitstream generation.

However, Xilinx does not provide the information of how a certain bit of the configuration frame can control a specific hardware function of the FPGAs. These kinds of details are provided for older FPGAs families only [143]. Nevertheless, in the last decade, a lot of works and projects reverse-engineered the bitstream structure of Xilinx FPGAs, allowing manipulation of the bitstream for custom applications (e.g., Replica [58] and Torc [109]).

Figure 2.4: Bitstream structure.

Figure 2.4 depicts the bitstream structure. The bitstream is composed of (1) a bitstream header, then (2) n Logic Frames Configuration according to the dimension of the device, (3) BRAMs frames and finally (4) the end of configuration.

As shown in Figure 2.4, every frame starts with one *Frame Address Register* (*FAR*), which allows determining the position of the frame inside the configuration memory. Even if it seems an overhead for a full bitstream, this property is remarkable when just some frames need to be configured. This is the case of a small design where unutilized frames do not need to be configured. Also, when DPR is performed, typically just some frames are reconfigured.

[125] provides all the information to create a bitstream, either full or partial. Table 2.2 in Section 2.1.6 shows the dimension of a full bitstream for each FPGA family.

The process of configuring an FPGA can be modeled in 4 sequential steps [142]:

- 1. *Setup*: consists in power up the device and clear the previous configuration memory.

- 2. Device initialization: initializes the state machine that loads the bitstream.

- 3. *Bitstream Loading*: is the process of writing all the frames in the correct position of the configuration memory. This process is controlled by the state machine.

- 4. *Startup*: is the phase where the loaded configuration is electronically implemented into the device. Hence, it can start to operate.

#### 2.1.5 Routing Physical Wires

INTs are connected among them using general purpose routing connections, which are called *physical wires* (*PWs*). In the following, these connections are classified, giving a better overview of the FPGA routing.

In all the Xilinx families considered in this work (Virtex-4, Virtex-5, Virtex-6, Spartan-6, 7 Series and Zynq), the PWs are divided into two main groups: *local PWs* and *long PWs*. The first type provides mostly connections with adjacent tiles. Instead, the long PWs are connections that span an extended portion of the FPGA, allowing direct connection among distant INTs.

The direction of these PWs is another aspect that differs in these two categories; the local PWs are unidirectional connection while the global PWs are bidirectional.

#### **Local Physical Wires**

As explained in Section 2.1.1, the connection point between a PW and an INT is called *wire*. In the specific, a wire is an *inWire* if the signal goes from the INT to the PW; in the opposite case, a wire is called *outWire*. According to this classification, it is possible to have two different PIPs: *inPIPs* and *outPIP*. In inPIPs the signal pass first through the PIP and then to the wire; in the opposite case a PIP is called outPIP.

In Figure 2.2 the outPIPs and inPIPs are depicted in purple and yellow respectively, according to the representation in FPGA Editor [128]. It is important to clarify that every PIP can be at the same time inPIP and outPIP; the classification is given with respect to the wire that is considered. Every PIP connects one inWire and one outWire, hence, considering the inWire the PIP is presented as an inPIPs; in the other case, respect to the outWire the same PIP is classified as an outPIP.

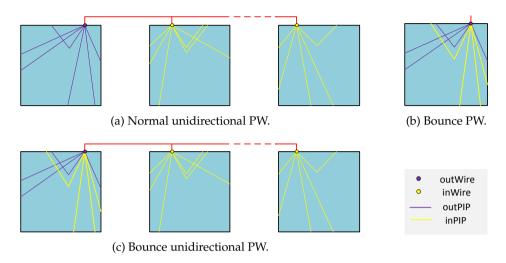

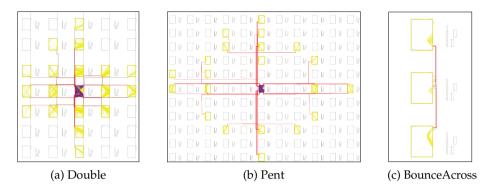

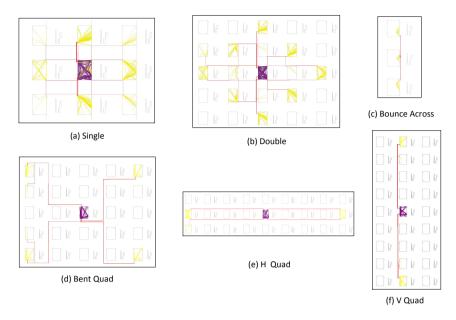

Figure 2.5 shows the different types of local PWs, which are:

- *Normal Unidirectional PW*: this type covers most of the FPGAs connections. These PWs are composed by one outWire connected to one or more inWires (Figure 2.5a). To the outWire of this PW type, only outPIPs are connected.

- Bounce Unidirectional PW: these PWs (see Figure 2.5c) are similar to the Normal Directional PW, except for the PIPs connected to the outWire; these are either of the outPIP or inPIP type. In this way, the wire can be used like a bounce PW (next PW type). So the signal it is not routed through the PW but the wire is just used to "bounce" the signal.

- Bounce PW: this PW (see Figure 2.5b) is composed by one outWire, where inPIPs and outPIP are connected to it. Therefore, these PWs can be used only like a bounce PW; passing through this wire is possible to reach another outWire of the same INT.

Figure 2.5: Xilinx FPGA PWs types. The light-blue boxes represent SMs, and the red lines represent the PWs.

#### **Long Physical Wires**

This PWs span a wider number of INTs. For example, in Virtex-4 long PWs span 24 INTs and in Virtex-6 they span 12 INTs. Their direction is either vertical or horizontal. In addition, they can route signal in both directions, differently from local PWs.

Often, long PWs create problems in a DPR system; the possible issues are:

- Reliability: in DPR systems, the FPGA is partitioned into static and reconfigurable areas. In this scenario, one of the main topic considered is the fault-tolerance of the system. Many works have investigated how a fault occurred in one area can affect another one. One of the ways to propagate errors is an unexpected configuration of a PIP. Therefore, in this case, if a PIP related to a long PW is activated, the error can be propagated to more reconfigurable areas, due to the intrinsic length property of long PWs.

- Inhomogeneity of DPR systems: as Section 3.2.1 presents, when a module is placed and routed (P&R) within a certain reconfigurable area, the tools verify that the resources are not utilized by other circuits. In most of the cases, the static design is configured, then reconfigurable modules are considered. In this kind of scenario, a PAR tool just needs to verify that the FPGA resources are not occupied by other circuits. A possible problem can occur in the case of module relocation. The bidirectional property of the long PWs gives to

Figure 2.6: Application Specific Modular Block (ASMBL) architecture.

the P&R other condition to consider; whenever a PR Module needs to be synthesized in an area of a particular type, for example *type A*, the PAR needs to verify in all the area of *type A* if no PWs are in conflict with the design. Therefore, a possible solution to avoid issues is to exclude the use of long PWs in the routing of a PR Module.

#### 2.1.6 Xilinx FPGA families

In this work, the Xilinx FPGAs are the target devices. These SRAM-based FPGAs offer advanced functionalities and allow the implementation of a single application on a single chip. Furthermore, these devices are partial homogeneous across different families and devices. In this thesis, all devices starting from the Virtex-4 family [144] are considered and studied. These devices, even if they are more than a decade old, are still used in many kinds of applications.

For example, the new Solar Orbiter satellite (presented in Section 3.3.2), has on board a radiation tolerant Virtex-4 device; it will be launched in 2018, and it will have a mission duration of 10 years. This gives the idea of how supported and valuable are these devices, even after more than a decade since their introduction in the market.

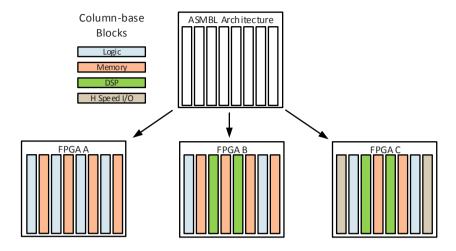

Xilinx started to utilize a new production method for their devices from the Virtex-4 family: the Application Specific Modular Block (ASMBL $^{TM}$ ) [84]. This kind of modular approach allowed Xilinx to produce multiple kinds of devices, which embed in some cases different dedicated hardware (e.g., PowerPC®, DSP).

ASMBL $^{TM}$  supports the concept of multiple domain-specific platforms through the use of a column-based architecture approach (presented in Figure 2.6). Each column represents a silicon sub-system with a specific capability (e.g., CLBs, BRAMs, IOBs, DSPs).

This has allowed having different kinds of devices in term of space and functionalities, enabling deployment of multiple domain-specific FPGAs to target different customers and different applications [84] (i.e., the customer can select a specific device with specific functionalities, avoiding buying an expensive device). The  $ASMBL^{TM}$  production method is still used for the latest Xilinx FPGAs produced.

Table 2.2 summarizes the main features and difference among the Xilinx FPGAs considered in this work: *Virtex-4, Virtex-5, Spartan-6, Virtex-6, and 7 Series*. In total, the devices considered are 207.

Within seven years, the maximum number of logic cells available in the device is ten times bigger, going from 200 k in Virtex-4 to 1,954 k in Virtex-7. Moreover, in newer families, Xilinx introduced fast I/O connections, i.e., high-speed transceiver and PCIe interfaces. This motivates the growing interest and used applications of these kinds of devices. In the following, properties of each FPGA family are presented.

#### Virtex-4

Virtex-4 devices [144], introduced in 2004, are produced on a 90 nm copper process. This family provides three different platform subfamilies of devices: *LX*, *SX*, and *FX*. The LX sub-family is oriented to applications that require high logic functionality; SX devices are oriented to high-performance solutions for DSP applications; FX FPGAs provide high-performance, full-featured for embedded platform applications. Virtex-4 FX FPGAs have on board 1 or 2 IBM PowerPC processors, RocketIO transceiver blocks.

As mention above, these devices have been the first produced with the ASMBL $^{TM}$  method. This has allowed providing 29 different FPGAs of the Virtex-4 family Table 2.2.

#### Virtex-5

In 2006, the Virtex-5 family was introduced [146]. These devices are built with a 65 nm CMOS technology using the second generation of  $ASMBL^{TM}$ . Like the Virtex-4 family, these devices are divided into subfamilies, according to their performance and dedicated embedded features.

Five subfamilies are available: LX, LXT, SXT, TXT, and FXT. LX subfamily is oriented to high-performance general logic applications. The letter T within the family name indicates the presence of Integrated Endpoint blocks for PCIe (x1, x4 or x8 supported) and Tri-mode 10/100/1000 Mb/s Ethernet MACs. LXT and

Table 2.2: Comparison of Xilinx FPGAs.

|                     | Virtex-4     | Virtex-5     | Spartan-6    | 6 Virtex-6    | 7 Series     |               |                |               |

|---------------------|--------------|--------------|--------------|---------------|--------------|---------------|----------------|---------------|

|                     | virtex-4     | virtex-3     | Sparian-0    | virtex-6      | Artix-7      | Kintex-7      | Virtex-7       | Zynq-7000     |

| Date                | 2004         | 2006         | 2009         | 2009          | 2011         | 2011          | 2011           | 2011          |

| Number of devices   | 29           | 41           | 45           | 28            | 27           | 18            | 20             | 17            |

| CMOS technology     | 90 nm        | 65 nm        | 45 nm        | 40 nm         | 28 nm        | 28 nm         | 28 nm          | 28 nm         |

| Logic-Cells         | 12 - 200 k   | Max 330 k    | 3 - 147 k    | 74 - 758 k    | 16 - 215 k   | 65 - 477 k    | 326 - 1954 k   | 28 - 444 k    |

| Max Block RAM       | 1 Mb         | 18 Mb        | 4.71 Mb      | 37.4 Mb       | 13 Mb        | 34 Mb         | 68 Mb          | 26.5 Mb       |

| Max DSP blocks      | 512          | 1,056        | 180          | 2,016         | 740          | 1,920         | 3,600          | 2,020         |

| Transceiver Blocks  | 0 - 24       | 0 - 24       | 0 - 8        | 0 - 72        | 4 - 16       | 8 - 32        | 28 - 72        | 0 - 4         |

| Max transc. Speed   | 6.5 Gb/s     | 6.5 Gb/s     | 3.2 Gb/s     | 11 Gb/s       | 6.6 Gb/s     | 12.5 Gb/s     | 28 Gb/s        | 12.5 Gb/s     |

| PCIe Interface      | x1 Gen1      | x8 Gen1      | x1 Gen1      | x8 Gen2       | x4 Gen2      | x8 Gen2       | x8 Gen3        | x8 Gen2       |

| Bitstream size (MB) | 0.6 - 6.1 MB | 0.8 - 9.9 MB | 0.3 - 4.0 MB | 3.1 - 18.7 MB | 2.1 - 9.3 MB | 2.9 - 17.9 MB | 13.3 - 45.9 MB | 2.0 - 16.6 MB |

SXT devices have RocketIO GTP transceivers (design to run from 100 Mb/s to 3.75 Gb/s). The subfamilies TXT and FXT have on board from 8 to 48 RocketIO GTX transceivers, which run from 150 Mb/s to 6.6 Gb/s. Finally, the FXT sub-family is the only one that mounts 1 or 2 PowerPC 440.

With respect to the previous family, Virtex-5 introduced a new general purpose routing structure (presented in Section 6.1). The modification consists of the introduction of a more dense routing structure, which allows having a diagonal connection to the INTs as well as horizontal and vertical. This permits the reduction of the Nets' latency, improving the overall performance of the system.

#### Spartan-6

Introduced in 2009, the Spartan-6 [137] targets applications with a low-power footprint, low-cost and high-volume availability. This family is built on a 45 nm process technology. This family provides a small form-factor packaging and a different number of supported I/O protocols. The logic cell density ranges from 3,840 to 147,443.

Two sub-families are available: *LX* and *LXT*. LX is oriented to applications that require mostly logic components; LXT version provides integrated Endpoint block for PCIe design and high-speed GTP transceivers (bandwidth up to 3.2 Gb/s).

#### Virtex-6

Introduced in 2009 (in parallel with the Spartan-6 family), Virtex-6 [149] is built with the third-generation of ASMBL $^{TM}$  column-based architecture. It is based on a 40 nm copper CMOS process. Starting from Virtex-6, no device is provided with embedded processors anymore; Soft IP-CORE microprocessors are available and can be programmed on the device.

28 different devices are produced, where logic cell capability varies from 74,496 to 758,784; the BRAM capability varies from 5.621 kb to 38.304 kb. All the devices provide up to 4 PCIe blocks, up to 4 Ethernet MACs connections and up to 48 GTX transceivers.

Virtex-6 is divided into three sub-families: *LXT*, *SXT*, and *HXT*. LXT provides high-performance logic with advanced serial connectivity; SXT targets signal processing capability with advanced serial connectivity; HXT mounts up to 25 GTH transceivers with a bandwidth up to (6.6 GB/s).

#### 7 Series

In 2011, 7 Series FPGAs [124] was introduced, which is built on a 28 nm high-k metal gate (HKMG) process technology. This family provides SelectIO technology with support for DDR3 interfaces up to 1,866 Mb/s. 7 Series unifies all the different

subfamilies of devices, under a main series (differently from the Spartan-6 and Virtex-6 family).

This has allowed having:

- Xilinx IP cores reused across all the 7 Series devices.

- Unified tools optimized for this kind of family; the new CAD flow Vivado [153] is introduced (provided in parallel to the ISE design flow, Section 2.3.1).

The series is divided into three families: *Artix-7*, *Kintex-7*, and *Virtex-7*. Artix-7 family can be seen as the updated version of the Spartan-6. Therefore, it targets the lowest cost and power consumption with small form-factor packaging. Kintex-7 is the mid-class family providing transceivers with a speed up to 12.5 Gb/s and logic cells up to 478 k. The Virtex-7 family provides the highest system performances (as the previous Virtex devices) and can have up to 1,955 k cells, up to 68 Mb of Block RAM, and transceivers with a speed up to 28.05 Gb/s.

#### Zynq-7000

Introduced in 2011, the Zynq-7000 family [163; 164] is based on the Xilinx All Programmable SoC architecture. These products integrate a Dual-Core ARM Cortex-A9 based processing system and a 28 nm Xilinx programmable FPGA in a single device (corresponding to the 7 Series architecture). The ARM Cortex-A9 CPUs include on-chip memory, external memory interfaces, and peripheral connectivity interfaces.

The Zynq-7000 family offers flexibility and scalability of an FPGA while providing performance, power, and ease of use device. These devices allow designers to target cost-sensitive as well as high-performance applications.

#### **UltraScale**

Introduced in 2013, the UltraScale family is the successor of the 7 Series family [140; 157; 158]. It provides up to 5.5 Logic Cells at 20nm. Similarly to the 7 Series family, they are divided into two sub-families:

- Kintex UltraScale: these devices focus on price/performance. They embed

a high number of DSPs, block RAM, and transceivers. They provide an

optimal tradeoff between capability and cost.

- Virtex UltraScale: these devices target the industry. The highest system capacity, bandwidth, and performance. Compared to the Kintex UltraScale, these devices provide higher system logic blocks, up to 5,541 (see Table 2.3), and up to 30.5 Gb/s transceivers.

Table 2.3: Comparison of UltraScale and UltraScale+ families FPGAs [162, pp. 1,26][141, pp. 18,19][141, pp. 878,879].

|                    | UltraScale           |                      | UltraScale+           |                       |                              |

|--------------------|----------------------|----------------------|-----------------------|-----------------------|------------------------------|

|                    | Kintex<br>UltraScale | Virtex<br>UltraScale | Kintex<br>UltraScale+ | Virtex<br>UltraScale+ | Zynq<br>UltraScale+<br>MPSoC |

| Date               | 2013                 | 2013                 | 2015                  | 2015                  | 2015                         |

| Number of devices  | 25                   | 24                   | 17                    | 22                    | 55                           |

| CMOS technology    | 20                   | 20                   | 16                    | 16                    | 16                           |

| Logic-Cells        | 318 - 1451 k         | 783 - 5541 k         | 356 - 1,143 k         | 862 - 3780 k          | 103 - 1143 k                 |

| Max Block RAM      | 75.9 Mb              | 132.9 Mb             | 34.6 Mb               | 94.5 Mb               | 34.6 Mb                      |

| Max DSP blocks     | 768 - 5520           | 600 - 2880           | 1368 - 3528           | 2280 - 12288          | 240 - 3528                   |

| Transceiver Blocks | 12 - 64              | 36 - 120             | 16 - 76               | 40 - 128              | 0 - 72                       |

| Max transc. Speed  | 16.3 Gb/s            | 30.5 Gb/s            | 32.75 Gb/s            | 32.75 Gb/s            | 32.75 Gb/s                   |

| PCIe Interface     | x8 Gen3              | x8 Gen3              | x8 Gen4               | x8 Gen4               | x8 Gen4                      |

| Bitstream size     | 15,3 - 46,0          | 23,9 - 123,0         | 14,7 - 34,7           | 25,5 - 76,4           | 5,3 - 34,7                   |

#### UltraScale+

Introduced in 2015, the UltraScale+ FPGAs based on 16Fin FET+ technologies [159]. Moreover, these devices provide UltraRAM blocks and PCie x8 Gen4 [140]. This family is divided into two FPGAs sub-families:

- Kintex UltraScale+: these devices have increased performance memory, providing the ideal mix of high-performance peripherals and cost-effective system implementation.

- Virtex UltraScale+: these devices have the highest transceiver bandwidth, highest DSP count, and highest on-chip memory available in the industry for the ultimate in system performance [140].

Another subfamily of the UltraScale+ family is the Zynq UltraScale+ MPSoC, which is explained in the following.

#### Zyng UltraScale+ MPSoC

Introduced in 2015, the Zynq UltraScale+ MPSoC is an all programmable SoC, successor of the Zynq-7000 [140; 159; 162]. This family integrates a 64-bit Qual-Core or Dual-Core ARM Cortex-A53 and Dual-Core ARM Cortex-R5 based processing system and Xilinx programmable logic UltraScale architecture in a single device.

They also include an on-chip memory, multiport external memory interfaces, and a rich set of peripheral connectivity interfaces.

This family is divided into three subfamilies [161]:

- CG devices: they are featured with a Dual-Core Cortex-A53 (Application Processor) and a Dual-Core Cortex-R5 real-time processing unit. These devices target industrial sensor fusion, motor control, and Internet of things (IoT) applications.

- EG devices: they feature a Qual-Core ARM Cortex-A53 platform running up to 1.5GHz (Application Processor) and with Dual-Core Cortex-R5 real-time processors, a Mali-400 MP2 graphics processing unit. These devices have specialized processing elements that can target 5G wireless infrastructure, cloud computing, and aerospace applications.

- EV devices: they are based on the EG devices presented above; in addition, they integrate H.264 / H.265 video codec capability that allows simultaneous encode and decode up to 4Kx2K (60fps). These devices are ideal for automotive ADAS, multimedia, and embedded vision applications.

#### 2.1.7 Space-Grade devices

Space is one of the target applications of FPGAs. Nowadays, the antifuse FPGAs are strongly utilized in space missions. Nevertheless, SRAM-based FPGAs are getting more and more utilized, as well as COTS FPGAs, in particular for missions with shorter lifetime and less critical constraints.

Reconfigurable space-grade products can be divided into two categories:

- *Radiation-Tolerant*: these SRAM-based FPGAs provide immunity to certain radiation effect and specific mitigation for others.

- Radiation-Hard: these SRAM-based FPGAs thanks to radiation-hardened process and radiation-hardened design, they are immune to the effects of radiations.

Xilinx provides qualified devices for space: the Virtex-4QV (Radiation-Tolerant) and the Virtex-5QV (Radiation-Hard). The main difference from the COTS devices is the production and qualification phase. They are fabricated on a thin epitaxial wafer and high-reliability ceramic flip-chip packaging technology. The resistance to radiations is validated using in-beam testing (equivalent of millions of device years in space radiation environment).

Nevertheless, it is important to mention that in space-grade devices, configuration memory and the high-level architecture is the same of COTS devices; this

allows a direct porting from commercial to space-grade devices. Moreover, the Xilinx design flows (e.g., ISE, EDK) are compatible with this space-grade devices.

These FPGAs offer the latest solution for addressing the needs of critical space missions where design changes can be accommodated late in the program or through reprogrammability, even after launch [135]. In the following, a description of the two Xilinx space-grade devices is given: Virtex-4QV and Virtex-5QV.

#### Virtex-4QV

*Virtex-4QV* family [136] was introduced in 2007. These devices provide immunity to Single-Event Latch-up (SEL) and high tolerance against SEU and TID. They fall in the category of space-grade radiation-tolerant devices. Xilinx provides four different FPGAs: the *XQR4VSX55*, *XQR4VFX60*, *XQR4VFX140* and *XQR4VLX200* [136]. As mentioned above, these devices correspond to a specific commercial device, sharing the same modular architecture and pin packaging (i.e., XC4VSX55, XC4VFX60, XC4VFX140 and XC4VLX200 [144]).

It is worth to mention that the configuration memory and configuration controller of FPGAs do not have specific mitigation techniques in the fabric phase. Hence, SEUs are mitigated thanks to specific mitigation techniques at application-level (e.g., Triple Modular Redundancy (TMR)).

#### Virtex-5QV

*Virtex-5QV* [135] is a rad-hard by design (RHBD) device. It is total immune to SEL and provides 1 Mrad(Si) [26, p. 227] TID performance. Introduced in 2010, this family consists of a unique device, the *XQR5VFX130*. This device provides all the new features introduced with the Virtex-5 family combined with a rad-had design technology. This device embeds Error Detection and Correction (EDAC) and autonomous write-back for high-performance block memory SEU mitigation.

The Virtex-5QV design utilizes dual-nodes latches that control write operations to memory cells. Writes occur only when both latches are enabled synchronously. This implementation offers 1,000 times the hardness to SEUs compared to the commercial FPGA version.

According to [156], SEU immunity in the configuration memory and control logic is defined regarding deployment in a GEO environment about a space platform that travels 36,00 km/day. Based on 35 Mbits of configuration memory that could be subject to SEUs, the FPGA suffers  $3.8 \times 10^{-10}$  error per bit per day.

#### RT Zyng UltraScale+ MPSoC

In 2016, Xilinx announced a family of radiation-tolerant devices, called RT Zynq UltraScale+ MPSoC [50]. Currently, a unique device is expected to be avail-

able in 2018: the RT ZU19EG [50]. This device corresponds to the commercial ZU19EG [140].

Differently from the previous Xilinx space-grade devices, this device is an all programmable SoC. The RT ZU19EG integrates a programmable logic part (PL) with 1143 k Logic cells (10 times more than the Virtex-5QV device) and a processing system (PS). The PS consists of an application processing unit based on a Qual-Core ARM Cortex-A53, a Real-Time Processor Unit based on a Dual-Core ARM Cortex-5, and a Mali-400 MP2 graphics Processing Unit.

# 2.2 Dynamic Partial Reconfiguration

As mentioned in Section 2.1, in the last two decades, the utilization of SRAM-based FPGAs increased in a wide range of applications, providing the possibility to reconfigure hardware circuits multiple times. Later, the requirements of the market increased, therefore, developers and researchers started to investigate the possibility to reconfigure just a portion of an FPGAs (e.g., change just a specific functionality of a circuit), without the need to reconfigure the rest of the system.

Then, dynamic partial reconfiguration has been introduced, which has allowed reconfiguring just a portion of the FPGAs having the rest of the device still operating; this property of FPGA is called *Dynamic Partial Reconfiguration* (also known as *Run-Time Reconfiguration*). It was introduced in the Xilinx devices in the late 90s, on the Xilinx XC6200 series [21].

DPR can be performed in two different approaches [63]:

- Module-based: it is performed partitioning the FPGAs in a certain number of portions (tiles or slots). In this way, a certain hardware component (called module), can be placed in one slots/tiles dynamically.

- Difference-based: this approach does not require any partitioning of the system; as the name indicates, it compares two different configurations, a based- and a target-bitstream. As results, just a bitstream that contains the differences from the base-bitstream to the target-bitstream is generated. This method is suitable when the differences between two configurations are small, allowing a reconfiguration just in specific parts of the FPGAs.

The first approach executes a reconfiguration in a certain portion of the FPGA area, without considering the previous configuration. On the contrary, when a DPR is provided with the difference-based method, the new partial bitstream depends on the previous configuration of the device.

After that researchers have started to evaluate and investigate this property [17; 27], Xilinx provided the first support for DPR in 2006; the Early Access Partial

Reconfiguration (EAPR) plug-in [127], based on the ISE design flow. This module-based approach allowed running DPR on the Virtex-2 and Virtex-4 devices.

With the wide integration and utilization of the EAPR flow, Xilinx provided from the version ISE 12.1 (2010) [34; 131] a direct integration of DPR in ISE/PlanAhead, presenting new methodologies and support for a wider range of FPGAs (Virtex-4, Virtex-5, Virtex-6, Artix-7, Kintex-7, and Virtex-7). This new approach is called *Xilinx PR* (see Section 3.2.1).

#### 2.2.1 Benefits

Dynamic Partial Reconfiguration (DPR) is a remarkable feature of FPGAs [34]; it gives the designer the ability to reconfigure a certain part of the FPGA at run-time without influence the other ones.

Utilizing DPR, a system can have the following benefits:

- Reduce cost: the device can be time-scheduled, configuring a specific functionality only when is required. This allows the adaptation of a smaller device, rather than have a bigger one with all the functionalities implemented.

- Change a design on the field: DPR increases the flexibility of the device, allowing updates to a certain functionality without changing the overall system.

- **Reduce power consumption**: power is always an important aspect to consider in electronic devices. The power consumption of an FPGA is usually divided in *I/O power, dynamic power* and *static power* [160]. On the one hand, dynamic power can be reduced, since that, just a needed application can be configured when is needed; this avoids having unused circuits powered-on on the device. On the other hand, static power can be reduced as well, utilizing a smaller device. Moreover, considering the overall power consumed by FPGA, the impact of static power consumption is increasing, as CMOS technology shrinks [**Kuon**; 132].

- Increase reliability (fault-tolerance): SRAM-based FPGAs can be affected by radiations, which can change the configuration of a circuit (radiation effect on FPGA is discussed in Section 2.4). Thanks to the DPR, when a soft error occurs, it can be easily corrected overwriting it (i.e., blind-scrubbing [18]).

- **Reduce memory requirement**: if the FPGAs needs to be multiple time reconfigured, one of the problems can be the space required for the bitstream; as discussed in Section 2.1.4, a bitstream can occupy up to 46 MB. DPR allows having just a set of partial bitstreams, which can be reconfigured according to a specific use scenario.

Moreover, a DPR scenario can bring benefits in the final design complexity. Even if the development of a DPR communication infrastructure needs a higher cost for the design implementation, on the contrary, the final design can be less complex than a static one. More details about the comparison between static and DPR designs are provided in [98].

# 2.2.2 FPGA partitioning

In the following, it is described how a DPR system can be partitioned. This section summarizes the work presented in [61]. As presented at the beginning of this section, DPR can be applied in two different approaches: *module-based* and *difference-based*.

Difference-based is utilized for small changes on a design. However, the module-base approach offers more features and capabilities. A system that adopts DPR is called Partial Reconfigurable System (PR System). Xilinx provides an extensive guide, which explains how module-based DPR can be created and utilized [131].

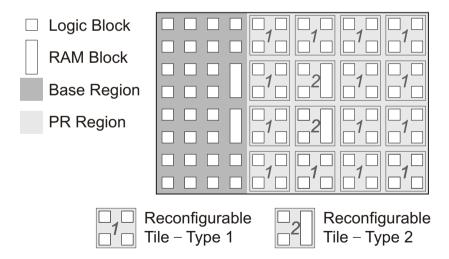

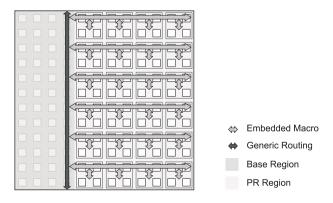

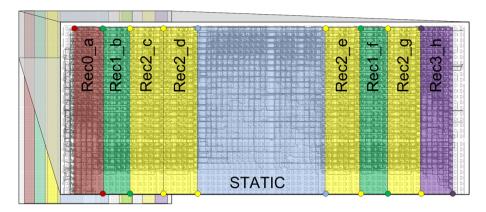

Figure 2.7 represents a heterogeneous FPGAs, which contains different logic blocks; in addition, it shows how a PR System can be created. A PR System design requires a partitioning of the FPGA to reconfigure only specific areas. In particular, two different regions are created: *base region* and *dynamic region* (also called Partial Reconfigurable Region (PR Region)). In Figure 2.7 they are indicated in dark-gray and light-gray respectively.

Figure 2.7: FPGA Partitioning using Partial Reconfigurable Regions (PR Regions) with Reconfigurable Tile [61].

The base region contains components that are not reconfigured. Therefore, the configuration of this region is made once in the initialization of the system, and it is not changed at run-time. On the contrary, the reconfigurable region is used for run-time reconfiguration; all the dynamic system components are located in this region.

To fully exploit the DPR capabilities, another partitioning of PR Region is required. A PR Region is divided in *Reconfigurable Tiles (PR Tiles)*, which are the smallest partial reconfigurable units in the system. According to the heterogeneity of the FPGAs, a PR Region may contain different types of PR Tiles, which contain different resources (e.g., CLBs, Block RAMs and DSPs). For example, in Figure 2.7, the PR Region is divided in PR Tiles of two different types.

The dynamic logic components are represented by the PR Modules, which can be placed and removed at run-time. The placement is done by reconfiguring suitable contiguous PR Tile. According to the PR Tile types, the PR Module can be placed in different position, using an equivalent configuration; this mechanism is called *bitstream*.

In this kind of scenario, the communication infrastructure is one of the key components, which allow communication among static regions and all the PR Tiles. Section 2.2.3 discusses in detail how a communication infrastructure, which allows relocation of PR Modules, can be created.

# 2.2.3 Communication Infrastructure in a PR system

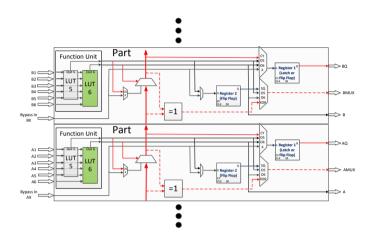

Communication infrastructure is a key part of a DPR design; it allows the interconnection of all the different areas of the system. Different communication infrastructures can affect the reconfigurable property of the system (e.g., homogeneity, interrupt free reconfiguration, dedicated signal). This section summarizes the communication infrastructure presented in [61].

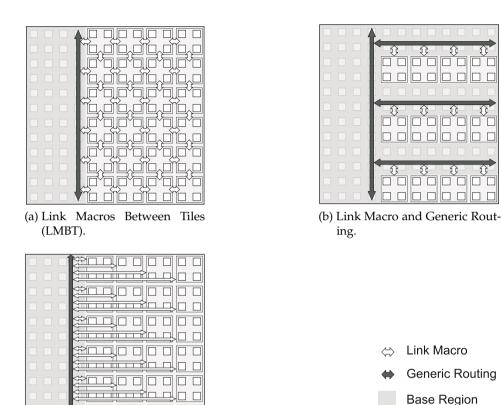

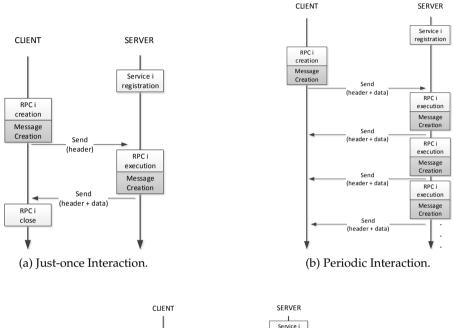

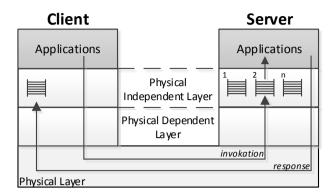

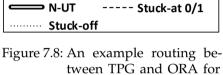

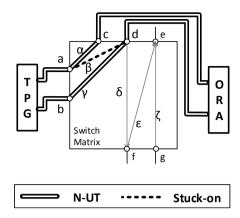

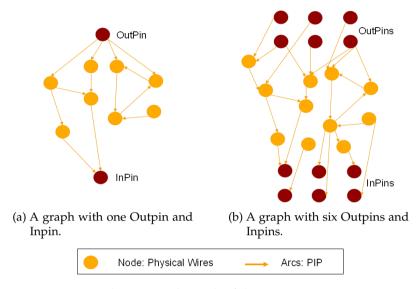

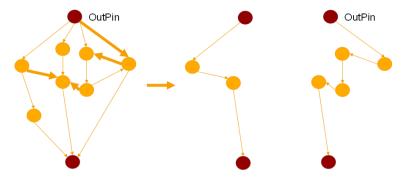

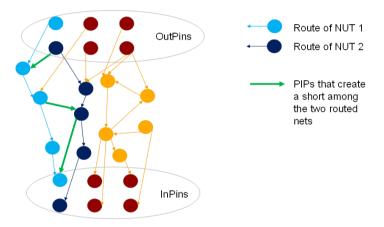

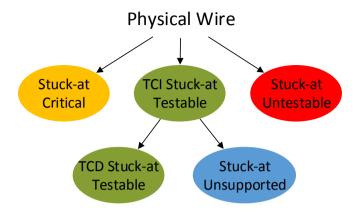

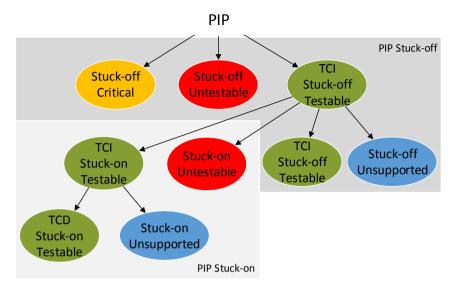

In 2006, with the EAPR flow [127], Xilinx provided the first approach to establishing communication between different areas (static or dynamic): the bus-macro [63]. Bus-macros are instances of the FPGA logic and routing resources. They are intended to lock the routing between different regions, making possible to connect the pins of either the static part or a PR Module. In this way, whenever a PAR is executed, the resources occupied by a bus-macro are reserved. Hence, in the EAPR plug-in, the bus-macros were the only communication channels crossing the reconfigurable regions.