#### Exzellenzcluster Cognitive Interaction Technology

Kognitronik und Sensorik Prof. Dr.-Ing. U. Rückert

# Dynamisch partielle Rekonfiguration in fehlertoleranten FPGA-Systemen

zur Erlangung des akademischen Grades eines

DOKTOR-INGENIEUR (Dr.-Ing.)

der Technischen Fakultät der Universität Bielefeld

genehmigte Dissertation

von

# Dipl.-Ing. Sebastian Korf

Referent: Prof. Dr.-Ing. Ulrich Rückert Korreferent: Prof. Dr. Christian Plessl

Tag der mündlichen Prüfung: 14.09.2017

Bielefeld / September 2017 DISS KS / 13

## **Danksagung**

An dieser Stelle möchte ich mich bei allen Personen herzlich bedanken, die mich während meiner Arbeit auf unterschiedlichste Weise unterstützt und zu meiner Dissertation beigetragen haben. Besonderer Dank gilt Prof. Dr.-Ing. Ulrich Rückert, der mir diese Dissertation ermöglicht und mich bereits als Studentische Aushilfskraft in Paderborn in seinem Fachgebiet Schaltungstechnik aufgenommen hat. Ein großer Dank gilt Dr.-Ing. Mario Porrmann, der mich zum Schritt der Promotion ermutigt hat und stets eine offene Tür und ein offenes Ohr für unzählige, wertvolle Diskussionen hatte. Insbesondere möchte ich mich für die konstruktive Rückmeldung zu dieser Dissertation bedanken. Ebenfalls möchte ich mich bei Prof. Dr. Christian Plessl für die Begutachtung dieser Dissertation bedanken.

Ein besonderer Dank gilt auch Jens Hagemeyer, der mich bereits seit der Zeit als Studentische Aushilfskraft betreut und anschließend über viele Jahre begleitet und geprägt hat. Ebenfalls möchte ich mich bei Dario Cozzi für die intensive Zusammenarbeit seit unserer Master-/Diplomarbeitszeit bedanken. Gemeinsam haben wir die Herausforderungen bei der Entwicklung von DHHarMa, INDRA 2.0 und OLT(RE)<sup>2</sup> angenommen und gemeistert.

Weiterer Dank gilt allen Mitarbeitern des Fachgebiets Schaltungstechnik und der Arbeitsgruppe Kognitronik und Sensorik für das gemeinschaftliche Arbeitsklima. Hierbei möchte ich mich insbesondere bei meinen beiden Studien-, anschließenden Arbeitskollegen und Freunden Martin Kaiser und Dirk Jungewelter für die vielen gemeinsamen Jahre mit fachlichen und nicht-fachlichen Diskussionen bedanken.

Zuletzt möchte ich mich bei meiner Familie für den starken Rückhalt und die Unterstützung bedanken. Der größte Dank geht an meine Frau, die mich seit meiner Jugend begleitet, anspornt und fördert sowie an meine beiden wundervollen Kinder, Lea und Ida, die mich stets auf Gedanken fernab von rekonfigurierbarer Hardware bringen. Euch widme ich diese Dissertation und bedanke mich für eure Liebe, Geduld und Nachsichtigkeit während der letzten Jahre.

# Kurzfassung

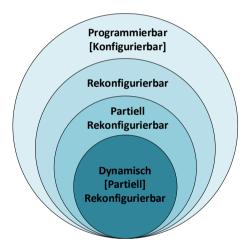

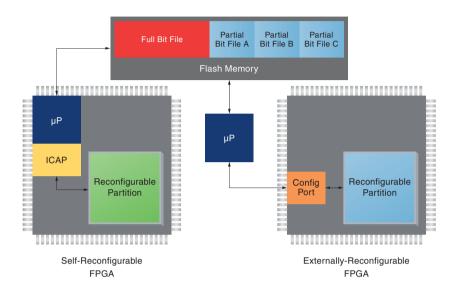

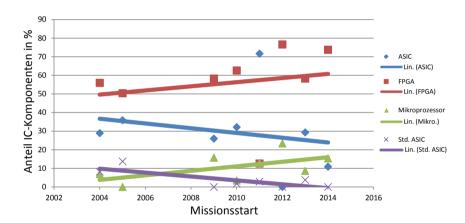

Die Anforderungen an mikroelektronische Systeme steigen kontinuierlich. Rekonfigurierbare Architekturen bieten einen Kompromiss zwischen der Leistungsfähigkeit anwendungsspezifischer Schaltungen (ASICs) und der Flexibilität heutiger Prozessoren. Sogenannte im *Feld programmierbare Gatter-Arrays* (engl. Field-**P**rogrammable **G**ate **A**rrays, FPGAs) haben sich hierbei in den letzten Jahrzehnten besonders etabliert. Die Konfigurationsart dynamisch partielle Rekonfiguration (DPR) moderner SRAM-basierter FPGAs verdeutlicht die gewonnene System-Flexibilität. DPR wird in verschiedensten Anwendungsgebieten aus unterschiedlichsten Motivationen heraus eingesetzt.

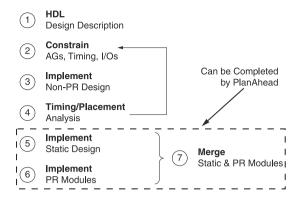

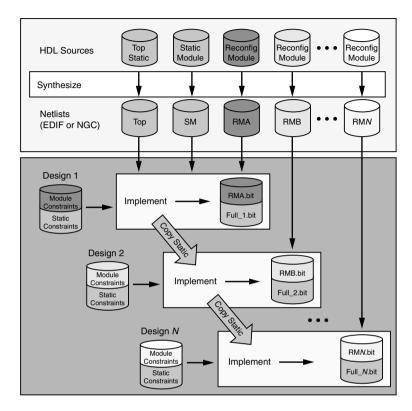

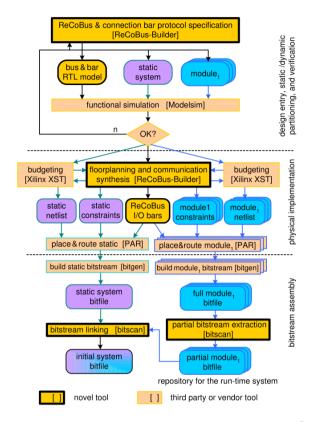

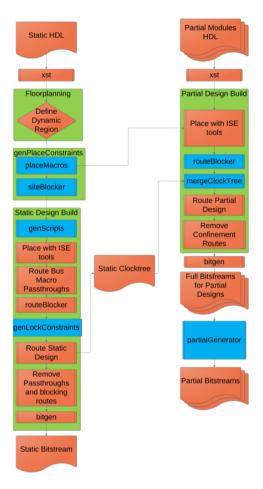

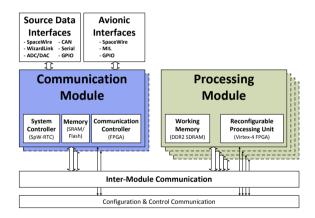

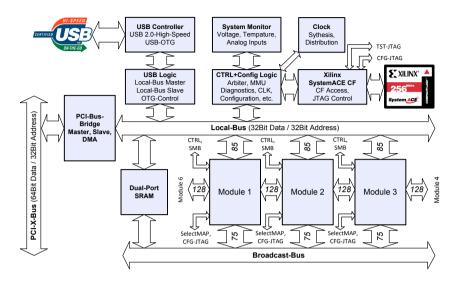

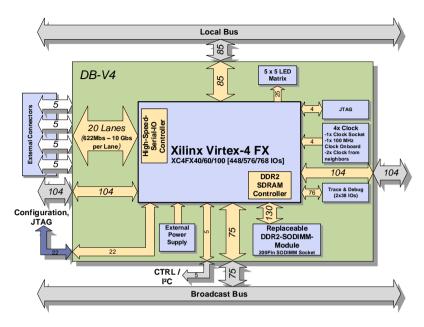

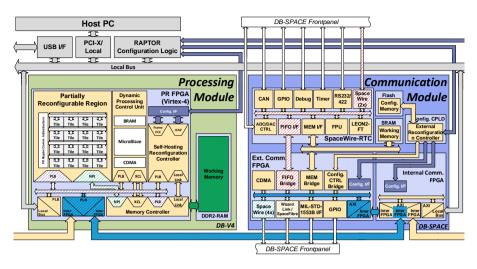

Die Hauptanwendung der DPR ist die Erstellung eines Systems, welches Veränderungen an der Schaltung auf dem FPGA zur Laufzeit erlaubt. Obwohl viele FPGA-Familien bereits seit zwei Jahrzehnten DPR hardwareseitig ermöglichen, ist die Unterstützung durch die Hersteller-Software und insbesondere die Eigenschaften des daraus resultierenden DPR-Systems verbesserungswürdig. Um das Potenzial der verfügbaren Hardware-Flexibilität ausnutzen zu können, wird in dieser Dissertation ein neuer Entwurfsablauf (INDRA 2.0, INtegrated Design Flow for Reconfigurable Architectures) vorgestellt. Dieser Entwurfsablauf ermöglicht die Erstellung eines flexiblen DPR-Systems mit geringem Speicher-, Verwaltungs- und Wartungsaufwand.

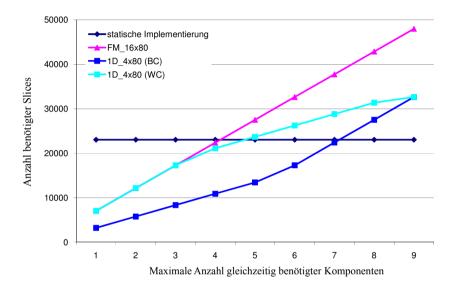

Für Anwendungen mit Homogenitätsanforderungen wird mit *DHHarMa* (*Design Flow for Homogeneous Hard Macros*) ein Entwurfsablauf vorgestellt, der die Transformation eines zunächst inhomogenen Designs in ein homogenes Design ermöglicht. Bei dieser Design-Homogenisierung ergibt sich die Fragestellung nach möglichen Auswirkungen bezüglich des FPGA-Ressourcenbedarfs und der Leistungsfähigkeit durch die einzelnen Homogenisierungsschritte. Die einzelnen DHHarMa-Softwarekomponenten wurden daher detailliert durch verschiedene Bewertungsmaße analysiert. Hierbei konnte festgehalten werden, dass die Homogenisierungsschritte im Mittel einen, teils deutlichen, positiven Einfluss auf den FPGA-Ressourcenbedarf jedoch teils einen geringen negativen Einfluss auf die Leistungsfähigkeit hat. Die verwendete FPGA-Architektur hat hierbei auf beide Größen einen entscheidenden Einfluss.

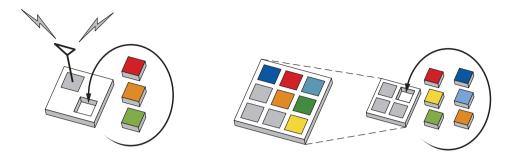

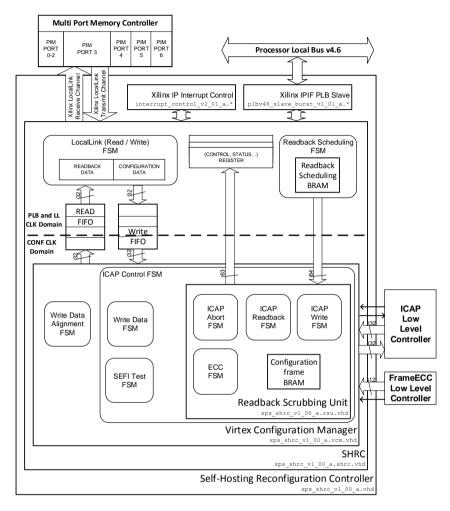

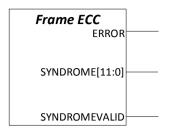

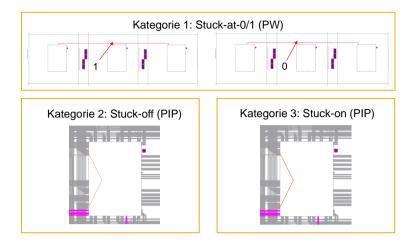

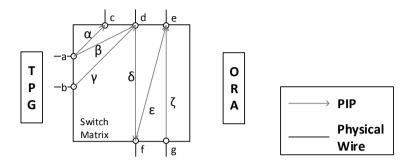

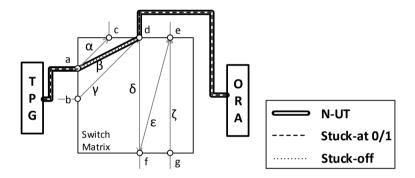

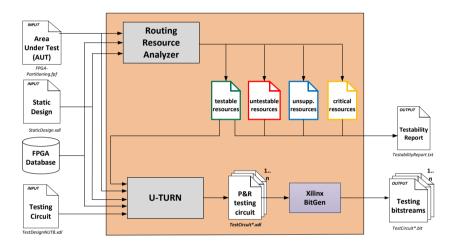

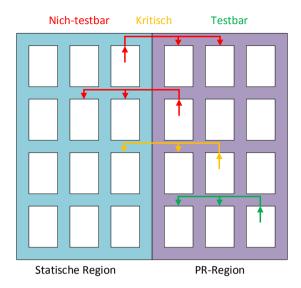

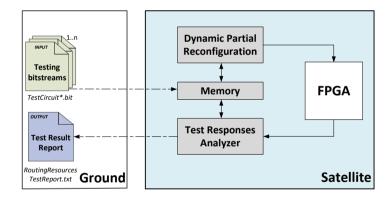

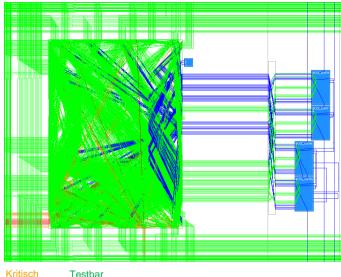

Zusätzlich wird in Anwendungsgebieten mit Strahlungseinfluss die DPR-Funktionalität in Verfahren zur Abschwächung von durch Strahlung induzierten Fehlern eingesetzt. In der Dissertation wird mit der Readback Scrubbing Unit eine Komponente vorgestellt, welche eine Einbitfehlerkorrektur und Zweibitfehlererkennung im FPGA-Konfigurationsspeicher implementiert. Durch integrierte Fehlerstatistikmechanismen wird eine Analyse des Systems zur Laufzeit realisiert. Zusätzlich ist die Erstellung von Readback Scrubbing Schedules möglich, sodass die Fehlererkennung und -korrektur zum einen autonom und zum anderen zur Laufzeit angepasst werden kann. Zusätzlich wird mit OLT(RE)² (On-Line on-demand Testing approach for permanent Radiation Effects in REconfigurable systems) ein Selbsttest für ein SRAM-basiertes FPGA vorgestellt. Dieser Selbsttest ermöglicht zur Systemlaufzeit eine Überprüfung einer FPGA-Fläche vor der Verwendung auf permanente Fehler in den Verdrahtungsressourcen.

# Inhaltsverzeichnis

| 1 | Einle | eitung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                |

|---|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|   | 1.1   | Inhaltlicher/Thematischer Überblick                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                |

|   | 1.2   | Motivation/Ziele                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                |

|   |       | 1.2.1 Erstellung eines flexiblen, feingranularen DPR-Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3                |

|   |       | 1.2.2 Erzeugung homogener Designstrukturen für FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                |

|   |       | 1.2.3 Erhöhung der Fehlertoleranz eines FPGA-basierten Systems .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                |

|   | 1.3   | Aufbau der Arbeit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                |

| 2 | Grui  | ndlagen zu FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7                |

| _ | 2.1   | Einordnung in und Vergleich mit bekannten Bauteilgruppen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                |

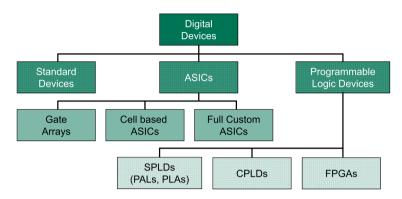

|   |       | 2.1.1 Einordnung in bekannte Bauteilgruppen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7                |

|   |       | 2.1.2 Vergleich von FPGA und ASIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10               |

|   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11               |

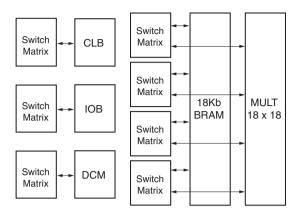

|   | 2.2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11               |

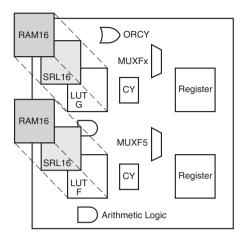

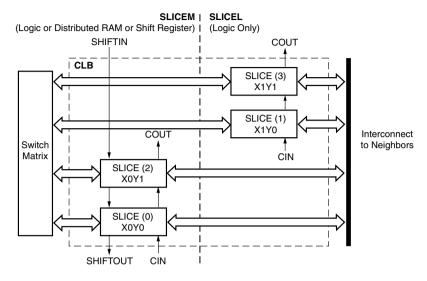

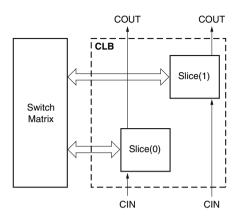

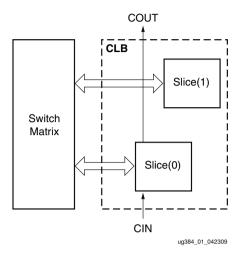

|   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12               |

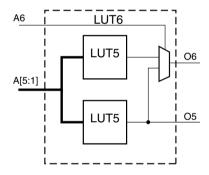

|   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14               |

|   | 2.3   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15               |

|   | 2.4   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18               |

|   | 2.5   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19               |

| 3 | Dyn   | amisch partielle Rekonfiguration von FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21               |

| Ŭ | 3.1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>-</b> .<br>21 |

|   | 0.1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22               |

|   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <br>24           |

|   | 3.2   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - ·<br>31        |

|   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31               |

|   |       | 3.2.2 Virtex-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33               |

|   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35               |

|   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36               |

|   |       | 3.2.5 7-Serie und Zynq-7000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37               |

|   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39               |

|   | 3.3   | The state of the s | 42               |

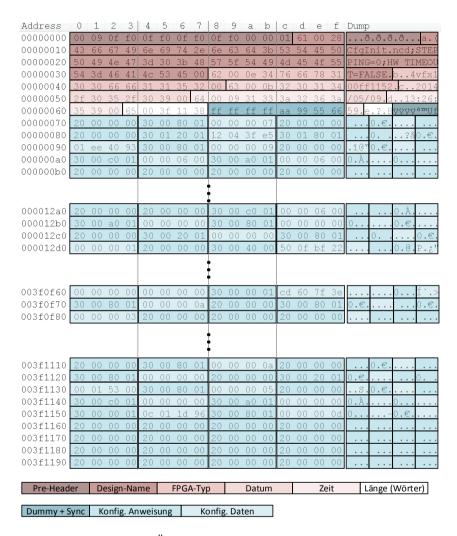

|   |       | 3.3.1 Konfigurationsspeicher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42               |

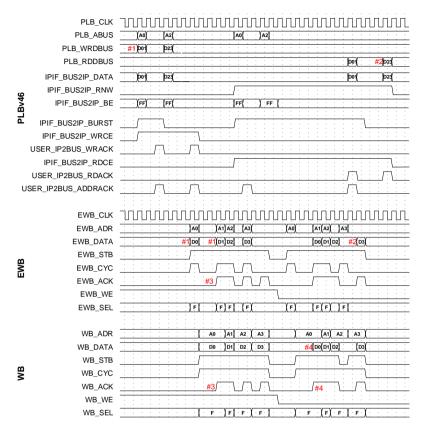

|   |       | 3.3.2 Konfigurationsschnittstellen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46               |

|   |       | 3.3.3 Konfigurationsablauf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49               |

|   |     | 3.3.4    | Dynamisch partielle Rekonfiguration eines Xilinx FPGAs    | 51  |

|---|-----|----------|-----------------------------------------------------------|-----|

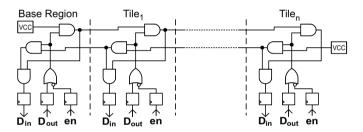

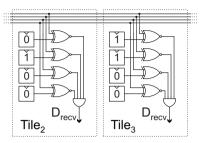

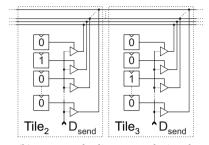

|   | 3.4 | Komm     | nunikationsinfrastrukturen in DPR-Systemen                | 56  |

|   |     | 3.4.1    | Eigenschaften der Kommunikationsinfrastruktur             | 56  |

|   |     | 3.4.2    | Typen der Kommunikationsinfrastruktur                     | 57  |

|   | 3.5 | Grob-    | und feingranulare DPR-Systeme                             | 62  |

|   |     | 3.5.1    | Rekonfigurationsarten                                     | 63  |

|   |     | 3.5.2    | Xilinx                                                    | 63  |

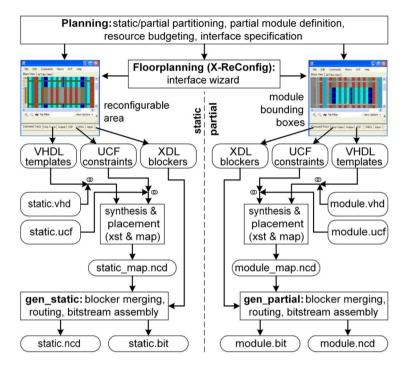

|   |     | 3.5.3    | ReCoBus und GoAhead                                       | 67  |

|   |     | 3.5.4    | OpenPR                                                    | 71  |

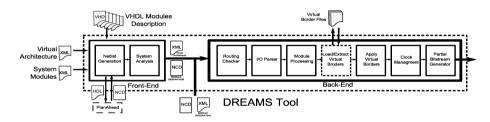

|   |     | 3.5.5    | DREAMS                                                    | 73  |

|   |     | 3.5.6    | INDRA                                                     | 75  |

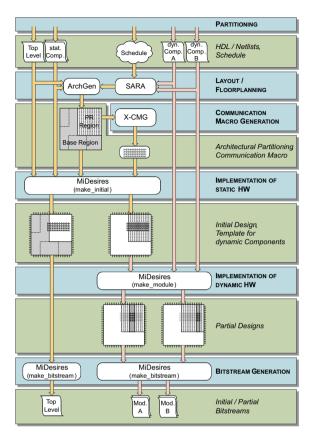

|   |     | 3.5.7    | INDRA 2.0                                                 | 77  |

|   |     | 3.5.8    | Vergleich der Ansätze                                     | 87  |

|   | 3.6 | Zusan    | nmenfassung                                               | 90  |

| 4 | חחח | larMa: / | Automatisierte Erzeugung homogener Strukturen für FPGAs   | 91  |

| 4 | 4.1 |          | ndungsgebiete mit homogenen Designanforderungen           | 91  |

|   | 1.1 | 4.1.1    | DPR-Kommunikationsinfrastrukturen                         | 92  |

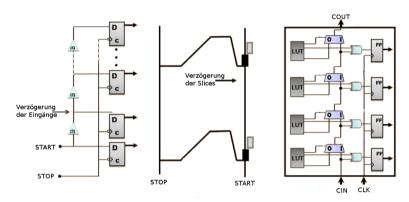

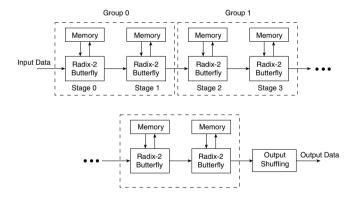

|   |     | 4.1.2    | Time-to-Digital-Converter                                 | 92  |

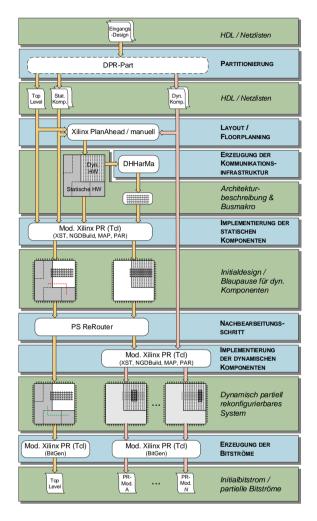

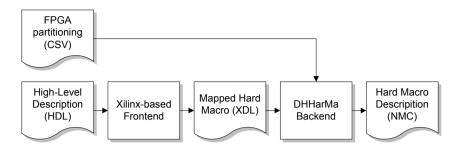

|   | 4.2 |          | ırfsablauf                                                | 93  |

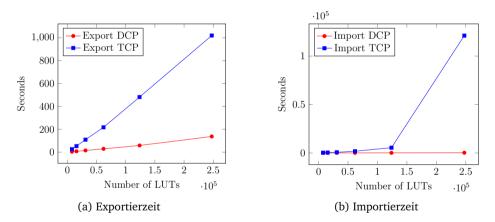

|   |     | 4.2.1    | Xilinx-basiertes Frontend                                 | 94  |

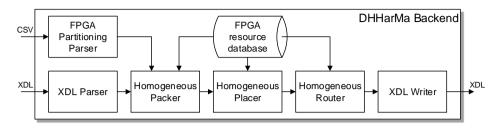

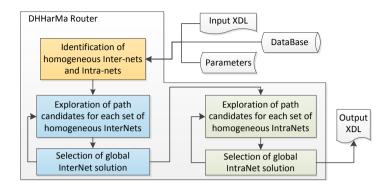

|   |     | 4.2.2    | DHHarMa Backend                                           | 95  |

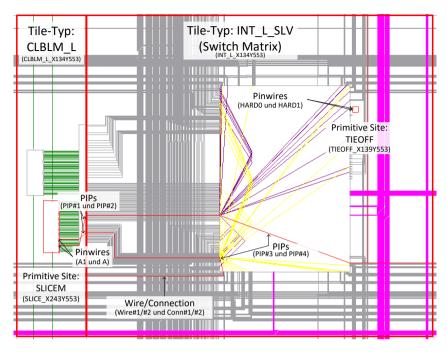

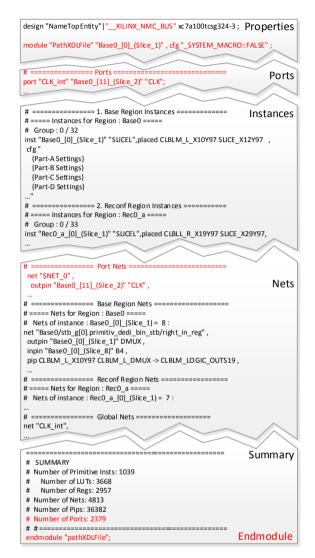

|   | 4.3 | Xilinx   | Design Language                                           | 96  |

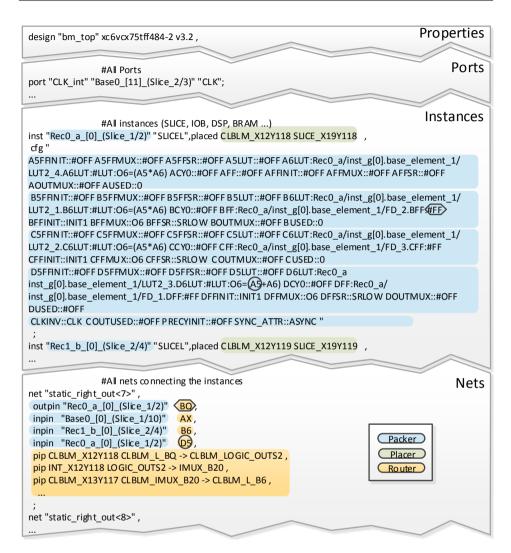

|   |     | 4.3.1    | XDL-Report                                                | 97  |

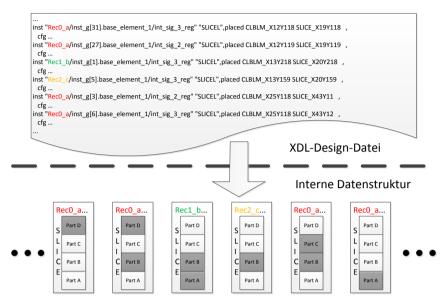

|   |     | 4.3.2    | XDL-Design-Datei                                          | 101 |

|   | 4.4 | HDL-E    | Bibliothek für DPR-Kommunikationsinfrastrukturen          | 104 |

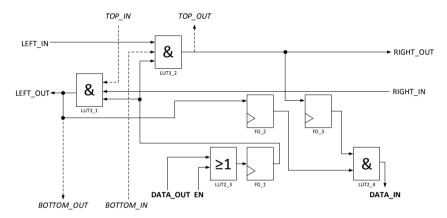

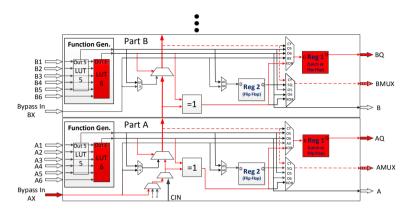

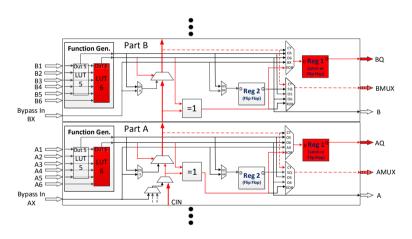

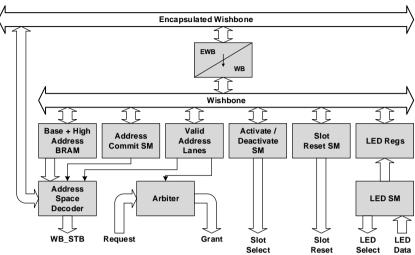

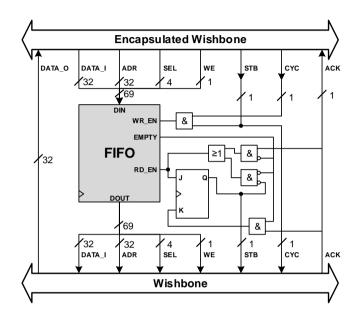

|   |     | 4.4.1    | Kommunikationsprotokoll Encapsulated Wishbone Bus         | 104 |

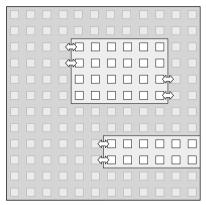

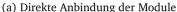

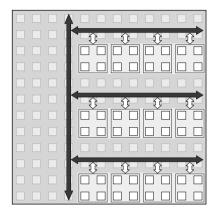

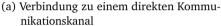

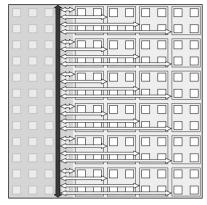

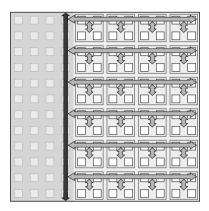

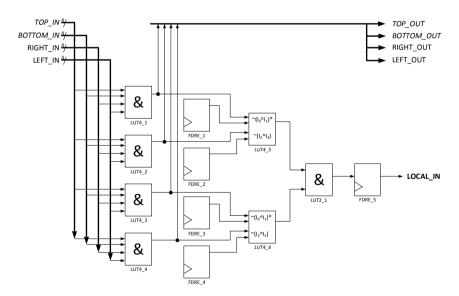

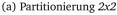

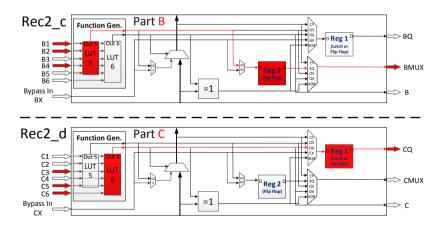

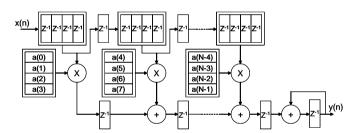

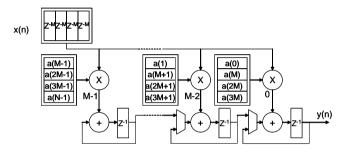

|   |     | 4.4.2    | Ein- und zweidimensionale Kommunikationsinfrastrukturen . | 106 |

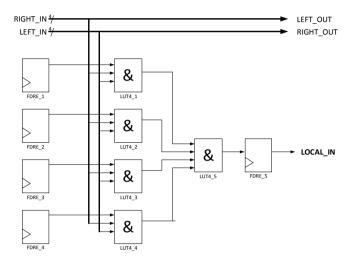

|   |     | 4.4.3    | Komponenten der Bibliothek                                | 108 |

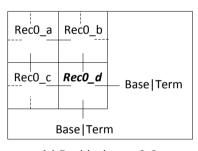

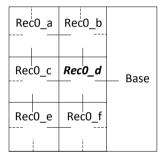

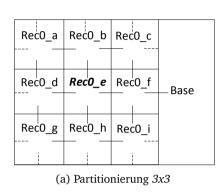

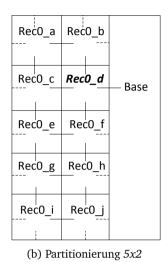

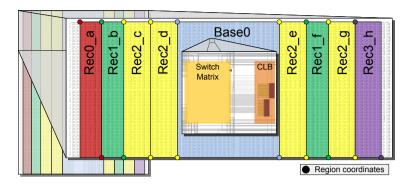

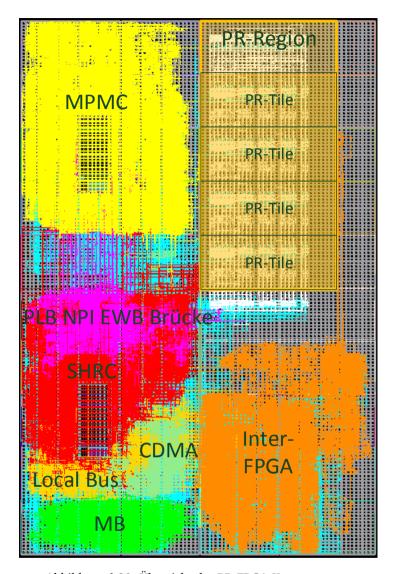

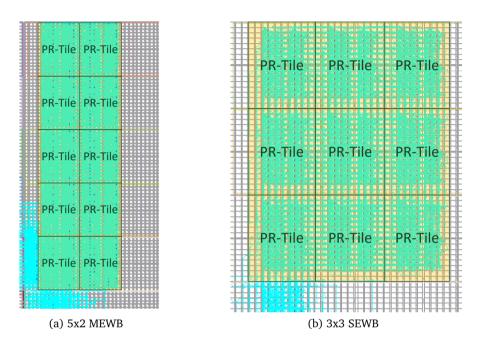

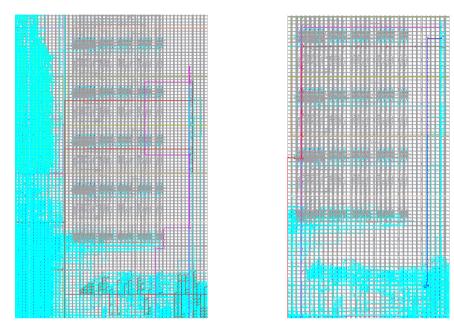

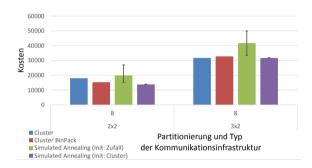

|   |     | 4.4.4    | DPR-Systempartitionierungen                               | 111 |

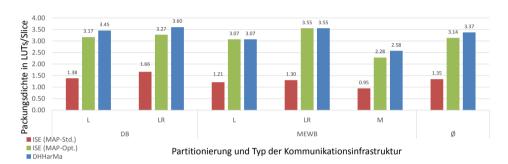

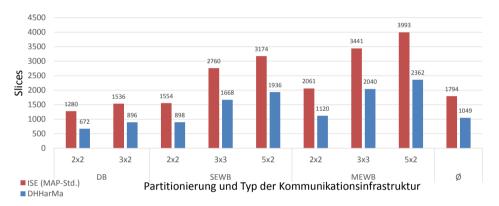

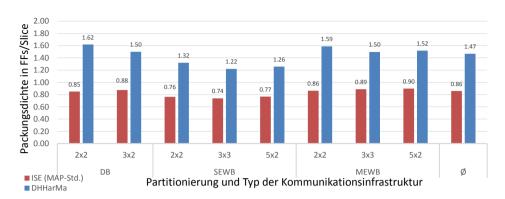

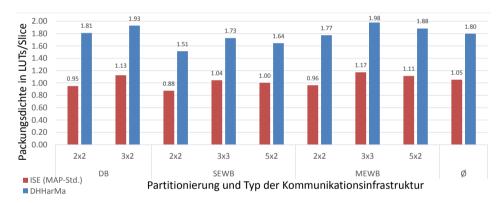

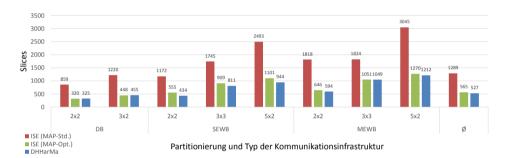

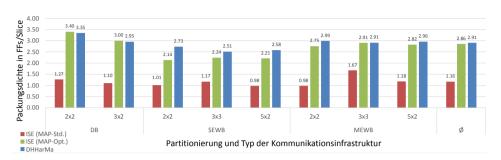

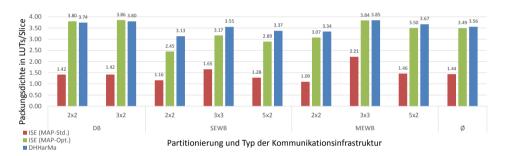

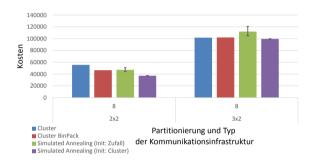

|   |     | 4.4.5    | FPGA-Ressourcenbedarf                                     | 114 |

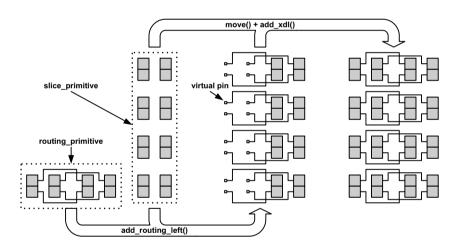

|   | 4.5 | Softwa   | arekomponenten des DHHarMa Backends                       | 117 |

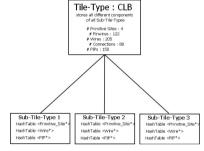

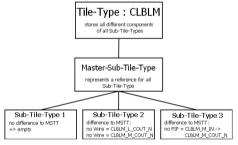

|   |     | 4.5.1    | Xilinx FPGA-Datenbanken                                   | 118 |

|   |     | 4.5.2    | Parser                                                    | 123 |

|   |     | 4.5.3    | Packer                                                    | 125 |

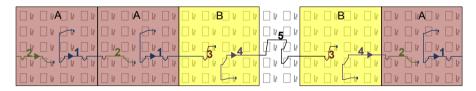

|   |     | 4.5.4    | Placer                                                    | 129 |

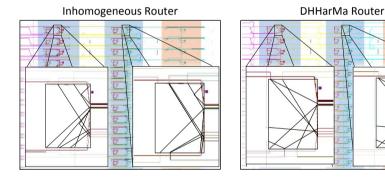

|   |     | 4.5.5    | Router                                                    | 134 |

|   |     | 4.5.6    | XDL Writer                                                | 136 |

|   | 4.6 |          | ertung                                                    | 138 |

|   |     | 4.6.1    | FPGA-Datenbanken                                          | 138 |

|   |     | 4.6.2    | Platzierungsalgorithmen                                   | 145 |

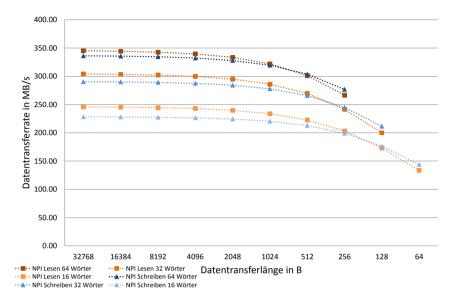

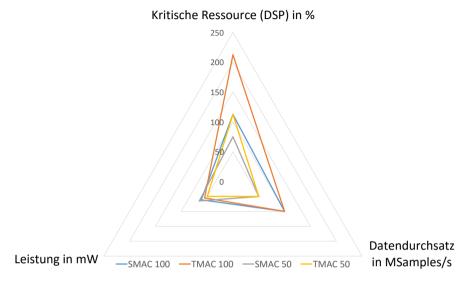

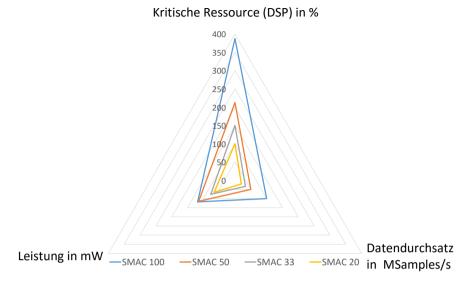

|   |     | 4.6.3    | DPR-Kommunikationsinfrastrukturen                         | 148 |

|   |                 | 4.6.4          | Time-to-Digital-Converter                                            | 16 |

|---|-----------------|----------------|----------------------------------------------------------------------|----|

|   | 4.7             | Zusam          | nmenfassung                                                          | 16 |

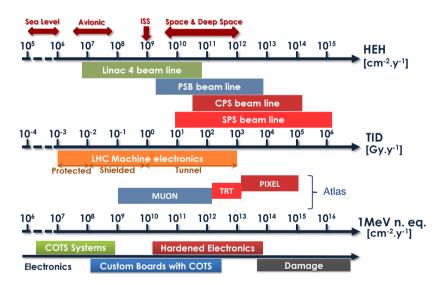

| 5 | Eine            | otz von        | FPGAs in Umgebungen mit Strahlung                                    | 16 |

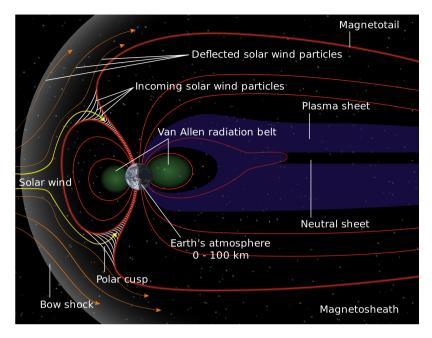

| , | 5.1             |                | ung in unterschiedlichen Umgebungen                                  | 16 |

|   | 3.1             | 5.1.1          | Kosmische Strahlung                                                  | 17 |

|   |                 | 5.1.2          | Terrestrische Strahlung                                              | 17 |

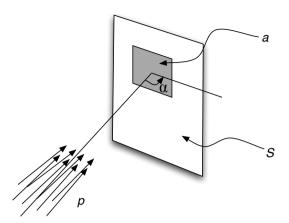

|   | 5.2             |                | schaften von Strahlung                                               | 17 |

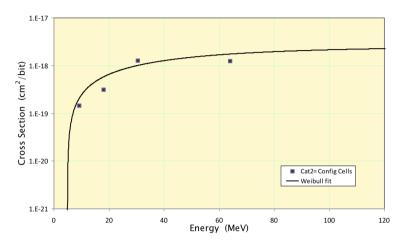

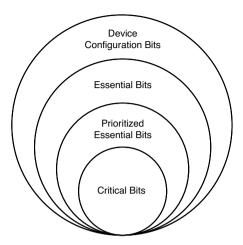

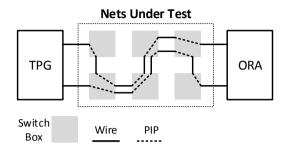

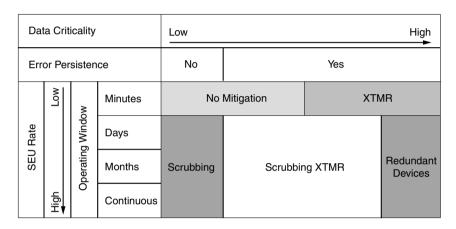

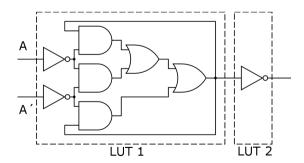

|   | 5.2<br>5.3      |                | calische Effekte durch Strahlung                                     | 17 |