# Novel Scheduling Strategies for Future NoC and MPSoC Architectures

## **DISSERTATION**

zur Erlangung des Grades eines Doktors der Naturwissenschaften

vorgelegt von Dipl.-Math. Christian Schöler

betreut von Prof. Dr. René Krenz-Bååth Prof. Dr.-Ing. habil. Roman Obermaisser

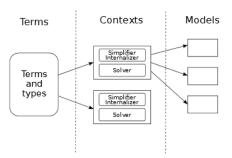

eingereicht bei der Naturwissenschaftlich-Technischen Fakultät der Universität Siegen Siegen 2017

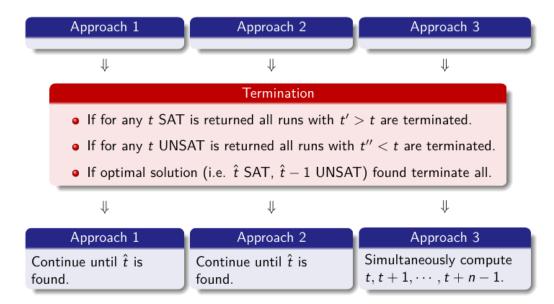

Datum der Disputation: 6. Juni 2017

gedruckt auf alterungsbeständigem holz- und säurefreiem Papier

## **Abstract English**

Time-Triggered Network-on-Chip (TTNoC) and Multi-Processor-System on a Chip (MPSoC) are networking concepts aiming at providing both predictable and high-throughput communication for modern multiprocessor systems. Time-triggered networks play an important role in safety-critical systems, where their inherent properties such as temporal predictability, fault tolerance and composability improve safety and reduce certification costs. Time-triggered networks use timeplans, which define the points in time of all message exchanges with respect to a global time base. In multi-cluster time-triggered systems of large embedded systems (e.g. automotive, avionics), conflict-free paths along switches and endsystems are defined for each message. The conflict-free temporal and spatial allocation of communication resources in combination with an intelligent communication network (e.g. local and central guardians) prevents interference between messages from different components upon integration and in the presence of faults.

Therefore, message scheduling in TTNoCs is one of the major challenges, where the points in time for the transmission of a message with conflict-free paths through the switches are determined. As the scheduling problem is  $\mathcal{NP}$ -complete this work introduces a novel scheduling framework based on the latest advancements of theorem solvers such as Satisfiability Modulo Theories (SMT) techniques which have successfully been applied to problem instances of this complexity class.

In addition, this work also investigates different concepts to partition the problem instances allowing the application of parallel computing to further accelerate the proposed scheduling framework.

MPSoC architectures and their specific architectural properties will require scheduling tools capable of dealing with the increasing complexity of the systems. To meet these challenges, we will outline how the proposed scheduling framework performs after it has been ported to an MPSoC emulating target system. We compare its performance to state-of-the-art schedulers based on CPLEX. Furthermore, we will analyze how the proposed scheduling framework can be deployed to recover from faults by re-scheduling the system under consideration at runtime.

## **Kurzzusammenfassung Deutsch**

Zur Erfüllung steigender Anforderungen hinsichtlich Sicherheit, Komfort und Effizienz an Mobilitätssysteme spielt die Elektronik eine immer größere Rolle. Dem daraus resultierenden Mehrbedarf an Performanz sowie der Reduzierung von Energieverbrauch, Größe und Gewicht können nur Multicoresysteme gerecht werden. Der Einsatz solcher Systeme in sicherheitskritischen Mobilitätsbereichen bringt allerdings noch viele offene Fragen mit sich:

Mit den steigenden Anforderungen an die Verfügbarkeit von Funktionen speziell in Zukunftsthemen wie (teil-)automatisiertem Fahren oder Internet of Things, müssen neue Architekturpattern, sogenannte Multi-Processor-Systems on a Chip (MP-SoCs), entwickelt werden. Diese Patterns sollen eine hochgradige Verfügbarkeit von Funktionen sicherstellen und gleichzeitig kostengünstig umgesetzt werden.

Eine der zentralen Fragestellungen für moderne Mehrkernarchitekturen ist eine effektive Umsetzung der internen Kommunikationsprozesse. Die vorliegende Arbeit präsentiert einen Scheduler, der optimale Zeitpläne berechnen kann und auch auf einem eingebetteten System mit eingeschränkter Rechenkapazität eingesetzt werden kann. Darüber hinaus diskutieren wir Strategien, um diesen Scheduler effizient einzusetzen. Als Grundlage für die Berechnung von optimalen Schedules nutzen wir moderne Tools aus der automatisierten Verifikationstheorie, da das optimale Scheduling Problem aus der Komplexitätsklasse der  $\mathcal{NP}-$ vollständigen Probleme stammt. Wir erläutern, warum Verifikationstools aus diesem Gebiet geeignet sind, um optimale Schedules für zeitgesteuerten Systemen, sogenannten TTNoCs, zu berechnen.

Der Einsatz dieser Programme bietet zwei zentrale Vorteilen gegenüber der herkömmlichen Berechnung mit Multi-Integer-Linear-Programming (MILP) basierten Schedulern: Zum einen können wir die Laufzeit und den Speicherbedarf reduzieren und auf der anderen Seite unser Scheduling Framework auch direkt auf dem MPSoC verwenden. Neben dem Einsatz auf dem Zielsystem evaluieren wir, wie unser Scheduler zur Laufzeit eingesetzt werden kann und die Fehlertoleranz des betrachteten Zielsystems verbessert. Dabei analysieren wir insbesondere die Performance unseres Schedulers im Vergleich zu einem weit verbreiteten heuristischen Ansatz.

# **Declaration of Authorship**

I hereby certify that this thesis has been composed by me and is based on my own work, unless stated otherwise. No other person's work has been used without due acknowledgement in this thesis. All references and verbatim extracts have been quoted, and all sources of information, including graphs and data sets, have been specifically acknowledged.

#### **Publications**

Below are listed the peer-reviewed publications that were published during the writing of this thesis between 2014 and 2016. Parts of the presented dissertation are based on these references. The contributions are listed in descending order of publication date:

- Christian Schöler, René Krenz-Bååth, Roman Obermaisser (2015). A Novel Formal Verification Framework for Future MPSoC Architectures. In *Proc.* on Manufacturable and Dependable Multicore Architectures at Nanoscale (MEDIAN/ETS) Workshop, co-located with DATE 2015, ISBN, Grenoble, France [1].

- Christian Schöler, Ayman Murshed, René Krenz-Bååth, Roman Obermaisser (2015). Optimal SAT-based Scheduler for Time-Triggered Networks -on-a-Chip. In *Proceedings of 10th IEEE International Symposium on Industrial Embedded Systems*, Siegen, Germany [2].

- Christian Schöler, Ayman Murshed, René Krenz-Bååth, Roman Obermaisser (2016). Computing Optimal Communication Schedules for Time-Triggered Networks Using an SMT Solver. In *Proceedings of 11th IEEE International Symposium on Industrial Embedded Systems*, Krakow, Poland [3].

- Christian Schöler, René Krenz-Bååth, Roman Obermaisser (2016). A Dominator-Based Partitioning for Efficient Scheduling in Time-Triggered NoCs. In *Proceedings of 42nd Euromicro DSD/SEAA 2016*, Limassol, Cyprus [4].

In addition, the topic of this thesis was accepted for poster presentation at the PhD Forum of IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC) in Tallinn, Estonia 2016. Our contribution can be accessed in the proceedings of the conference:

Christian Schöler, René Krenz-Bååth, Roman Obermaisser (2016). Novel Scheduling Strategies for future NoC and MPSoC Architectures. In Proceedings of 24th IFIP/IEEE International Conference on Very Large Scale Integration, Tallinn, Estonia [5].

#### Acknowledgements

First of all, I owe thanks to my doctor-fathers Professor René Krenz-Bååth and Professor Roman Obermaisser for suggesting this interesting research topic, for their endless patience and for letting me pursue the topic so freely. Furthermore, I want to express my gratitude to the Hochschule Hamm-Lippstadt (HSHL), University of Applied Sciences, for funding my work and giving all organizational support required. Furthermore, I wish to take the opportunity to thank Microsoft Research and Princeton University for their generous financial sponsorship allowing me to attend the Conference for Computer Aided Verification (CAV) in Toronto in July 2016.

I also wish to express my gratitude explicitly to Prof. Klaus Zeppenfeld and Karl-Heinz Sandknop representing the Board of HSHL for funding this research project over 36 months. Also I want to thank all members of HSHL-staff for their continuous and passionate support over the past three years. Without their help I would not have been able to realize this thesis.

In the same way I also want to mention my colleagues from the Fachgruppe Embedded Systems at Siegen University who supported my studies in every possible way. Not only did they kindly grant access to all their facilities but also made me feel at home whenever I visited. Special credit is of course given to Ayman Murshed, my respected co-author of two publications, whose expert knowledge on CPLEX was absolutely valuable for my work. Also I want to thank Hamidreza Ahmadian for giving me a detailed introduction into the models we consider in the scope of this work.

Obviously this project would have been impossible without the constant, caring and reassuring support of my family, especially my wife Sarah, my parents and my parents-in-law. They were always helping out and found the time to look after our son Julian, who is of course a precious gift and has been a valuable source of diversion whenever needed.

Finally, this work was partially supported by the European project DREAMS under the Grant Agreement No. 610640. Thank you.

VI CONTENTS

# **Contents**

| 1 | Intr | oduction                                         | 1          |

|---|------|--------------------------------------------------|------------|

|   | 1.1  | Motivation                                       | 1          |

|   | 1.2  | Problem Statement                                | 2          |

|   | 1.3  | Thesis Contribution                              | 2          |

|   | 1.4  | Methodology                                      | 3          |

|   | 1.5  | Thesis Structure                                 | 4          |

| 2 | Stat | e-of-the-Art                                     | 5          |

|   | 2.1  | Applications of Embedded Systems                 | 5          |

|   | 2.2  | SoC, NoC and MPSoC Architectures                 | 6          |

|   | 2.3  | Time-Triggered Communication Protocol            | g          |

|   | 2.4  | Scheduling in Time-Triggered Distributed Systems | 10         |

|   | 2.5  | MILP-based Scheduling                            | 12         |

|   | 2.6  | Related Work                                     | 13         |

| 3 | Con  | cepts and Terms                                  | 16         |

|   | 3.1  | Boolean Functions and their representations      | 16         |

|   | 3.2  | Optimization                                     | 25         |

|   | 3.3  | Complexity                                       | 31         |

|   | 3.4  | SAT Solving                                      | 34         |

| 4 | An ( | Optimal SAT based Scheduler                      | 38         |

|   | 4.1  | Introduction                                     | 38         |

|   | 4.2  | System Model                                     | 38         |

|   | 4.3  | MiniSat+                                         | 43         |

|   | 4.4  | Results                                          | 47         |

|   | 4.5  | Summary                                          | 51         |

| 5 | An ( | Optimal SMT-based Scheduler                      | <b>5</b> 3 |

|   | 5.1  | Introduction                                     | 53         |

|   | 5.2  | SMT Solving                                      | 54         |

|   | 5.3  | Refinements and Implementation                   | 60         |

|   | 5.4  | Application of YICES SMT                         | 67         |

|   | 5.5  |                                                  | 69         |

|   | 5.6  | Execution on MPSoC-emulating target systems      | 70         |

|   | 5.7  |                                                  | 73         |

| CONTENTS   | VII  |

|------------|------|

| CONTIDINID | V 11 |

| 6 | Para        | allel Computation of Schedules               | 75  |

|---|-------------|----------------------------------------------|-----|

| U | 6.1         | Introduction                                 | 75  |

|   | 6.2         | Parallel Checks for Satisfiability           | 75  |

|   | 6.3         | Results                                      | 78  |

|   | 6.4         | Dominator-based Partitioning                 | 80  |

|   | 6.5         | Results                                      | 88  |

|   | 6.6         | Summary                                      | 90  |

| 7 | Sche        | eduling on Fault-Tolerant Architectures      | 92  |

|   | 7.1         | Introduction                                 | 92  |

|   | 7.2         | Introduction into Fault Tolerance Techniques | 92  |

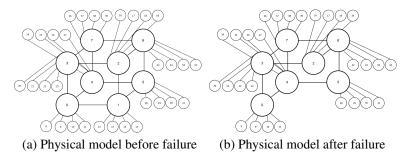

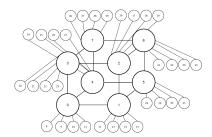

|   | 7.3         | Re-scheduling after Failure                  | 94  |

|   | 7.4         | List Scheduling                              | 96  |

|   | 7.5         | Results                                      | 101 |

|   | 7.6         | Summary                                      |     |

| 8 | Con         | clusion                                      | 108 |

|   | 8.1         | Summary                                      | 108 |

|   | 8.2         | Open Problems and Future Work                | 109 |

| A | App         | endix                                        | 111 |

|   | <b>A.</b> 1 | List of Figures                              | 111 |

|   | A.2         | List of Tables                               |     |

|   | A.3         | List of Abbreviations                        | 114 |

|   | A.4         | References                                   | 115 |

# 1 Introduction

#### 1.1 Motivation

This thesis is located in the field of multicore architectures implemented on a single chip like Multi Processor System-on-Chip (MPSoC) based on Network-on-Chip (NoC). NoC and MPSoC started a new computing era but brought a twofold challenge: On the one hand a new hardware paradigm emerged which required a layout pattern easy to use for software designers. On the other hand efficient NoC and MPSoC architectures require efficient software capable of utilizing the full potential of the high degree of parallelisation. Crucial to both research issues is the provision of a powerful communication infrastructure on the architectures under consideration. This work focuses on NoC and MPSoC architectures deploying a time-triggered communication protocol and introduces a novel scheduling framework providing optimal schedules by applying verification engines such as Boolean satisfiability (SAT) solvers and Satisfiability Modulo Theories (SMT) solvers.

Efficient scheduling on time-triggered NoC and MPSoC architectures is a prominent research subject especially as multicore chips play an important role in safety-critical systems, where their inherent properties such as temporal predictability, fault tolerance and composability [6] improve safety and reduce certification costs [7]. Time-triggered networks on and off chip use timeplans, which define the points in time of all message exchanges with respect to a global time base. In multi-cluster time-triggered systems of large embedded systems (e.g., automotive, avionics), conflict-free paths along switches and endsystems are defined for each message. The conflict-free temporal and spatial allocation of communication resources in combination with an intelligent communication network (e.g., local and central guardians) prevents interference between messages from different components upon integration and in the presence of faults.

However, the computation of the timeplans is time consuming and computationally complex [8]. Feasible schedules need to avoid conflicts of communication resources, meet deadlines, satisfy precedence constraints and ensure implicit synchronization [9]. Different optimal and heuristic scheduling algorithms have been devised in the state-of-the art (e.g. enumerative methods, mathematical programming, simulated annealing, genetic algorithms, tabu search, neural networks). While heuristics often fail to find feasible schedules, the runtime of optimal algorithms becomes prohibitive upon large problem sizes. This is due to the fact that computation of optimal schedules is one of the hardest problems in algorithmic and one of the first problems proven to be  $\mathcal{NP}$ -complete.

In order to address this challenge we introduce a communication model which

allows the application of the latest advances in SAT and SMT-solving which have undergone tremendous progress in the past two decades. SAT and SMT solvers are the backbone of a wide range of academic and industrial research activities and are widely used to tackle complex mathematical problems. On their basis optimal schedules can be computed in reasonable time for different types of MPSoCs.

There are various fields of applications for time triggered NoC and MPSoC architectures in industry for instance in (safety-critical) embedded systems in the automotive industry [10] as well as in academia [11]. Different types of embedded time-triggered execution platforms can be distinguished in practice [12, 13, 14].

#### 1.2 Problem Statement

The main purpose of this work is the development of a scheduling framework tailored to meet the tremendous complexity of evolving NoC and MPSoC architectures and their specific architectural properties. As modern NoC and MPSoC architectures are highly parallel systems an efficient communication infrastructure is of vital importance. In this thesis we optimize the schedule with respect to the given system requirement of minimizing the end-to-end latency. We can also formulate this by referring to the minimal transmission time for all messages or the minimal makespan. We introduce a model which allows the application of state-of-the art tools from the area of hardware verification like SAT and SMT to find optimal schedules.

Finding optimal schedules is one the most complex problems in computer science and is known to be  $\mathcal{NP}$ -complete. Therefore, we also analyse the tradeoff between optimal solutions which may be costly to compute in terms of runtime and heuristical methods which may be fast to calculate but result in a larger end-to-end-latency.

#### 1.3 Thesis Contribution

This thesis contributes to the field of design, implementation and verification of Multi-Processor System-on-a-Chip (MPSoC) architectures realizing embedded real-time systems. We develop a concept to deploy a set of SAT and SMT solvers to meet two different challenges: On the one hand we want to guarantee safety after reconfiguration and on the other hand we can find optimal solutions at runtime for scheduling problems within a network, which allows tolerating failing nodes or broken links and guarantees correctness within a given interval. Finally the proposed framework has successfully been ported to an architecture resembling an embedded real-time system.

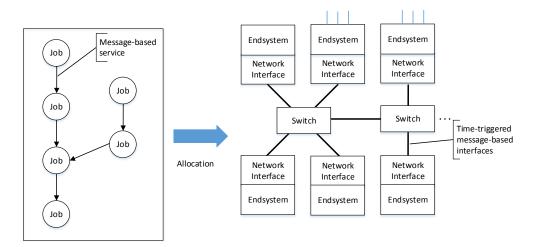

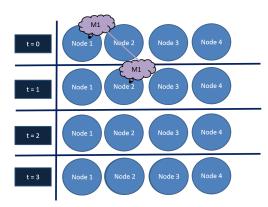

For a set of tasks depending on each other and represented by a directed acyclic graph, we present a model where the scheduling for endsystems and switches can be combined to find an optimal solution with respect to total transmission time. As the scheduling problem is  $\mathcal{NP}$ -complete we investigate different methods to improve scalability in order to apply the proposed framework to novel NoC and MPSoC architectures.

At first we model the properties of the scheduling problem in a way to apply modern SAT and SMT solvers respectively. We compute optimal schedules for different systems under consideration. Furthermore, the generation of benchmarks arising from scheduling problems on TT-NoCs is outlined and it is explained how the solvers can be applied either during the design process or on the target system itself. By enabling scheduling at runtime we increase the fault tolerance of the system under consideration. We can increase the flexibility to recover from faults by rescheduling the all required tasks if a component (i.e. an endsystem, a switch or a communication link) fails at runtime. For demonstrating purposes we use an MPSoC emulating target system.

We will report on the evaluation of performance and scalability of the proposed scheduler and suggest different techniques to tackle the  $\mathcal{NP}$ -complete optimal scheduling problem such as parallelising certain algorithmic instances or relaxing optimality constraints. We will compare runtime and resource requirements of the proposed framework with state-of-the-art-tools such as as the MILP tool CPLEX. Furthermore, we will demonstrate how the proposed scheduler can significantly improve the quality of schedules in comparison to a state-of-the-art approach deploying the popular list-scheduling heuristic if components of the system under investigation become faulty.

# 1.4 Methodology

After providing the theoretical background on propositional logic, optimization and complexity theory we develop a time discrete model which resembles the communication of the system under consideration. We will then outline how the scheduling problem can be formulated as an optimization problem with constraints and an objective function which is minimized in order to compute the minimal makespan i.e. the shortest possible transmission time for all messages. We will use SAT and SMT solver to compute optimal schedules and verify the solutions using Mixed integer linear programming. We will evaluate the results with respect to runtime and memory footprint and illustrate how the performance of our proposed scheduling framework can be further enhanced by the applying parallelisation.

Due to  $\mathcal{NP}$ -completeness of the scheduling problem we will also analyse strategies

to partition problems and compute feasible - not necessarily optimal - solutions in parallel.

Finally, we will also evaluate the proposed scheduling framework by comparing it to a scheduler based on heuristical methods called list scheduling (LS). We will apply both schedulers to a fault-tolerant MPSoC architecture and show how our proposed scheduling frameworks outperforms LS with respect to a minimal makespan if the number of faulty components in the system under consideration is increased significantly.

#### 1.5 Thesis Structure

This thesis is structured as follows: In the first Chapter we have already outlined the motivation, objective and contribution of this thesis as well as the methodologies applied.

In Chapter 2 introduces the technical background against this thesis is set. It describes the current state-of-the-art of requirements, challenges and applications of so called real-time embedded systems which become increasingly complex and are crucial for the implementation of safety-critical systems.

Chapter 3 then lays the mathematical and algorithmic foundations needed to model the scheduling problem as an (pseudo-Boolean-)optimization problem. Here we discuss all preliminaries regarding Boolean functions, mathematical optimization and complexity theory.

Chapter 4 we will demonstrate how the scheduling problem can be modelled in a way that allows the application of SAT-solving techniques to compute optimal solutions. The results are verified and evaluated using state-of-the-art tools.

On this basis Chapter 5 discusses enhancements to the proposed model and motivates the use of SMT solvers which are a generalization of SAT solvers. After further evaluation the SMT-based scheduling framework is ported to an MPSoC evaluating target system.

Two possible techniques to parallelize the solving process are discussed in Chapter 6. Both approaches have a significant impact on the runtime of the solvers.

In Section 7 we introduce the concept of fault tolerance and illustrate the advantages of the proposed scheduling framework if components of the architecture under consideration are subject to permanent failures. We will outline how critical deadlines can still be met thus sustaining functionality.

Finally Chapter 8 concludes this thesis and summarizes the results of our contribution. We also provide an outlook on how open problems may be tackled in future.

#### 2 State-of-the-Art

This introductory chapter outlines the technological background in which this thesis is set. We will describe the current state-of-the-art in theory and application of distributed embedded computer systems, which are realized using time-triggered communication networks. In this context the structural elements of an embedded computer system with a time-triggered communication network are explained and a terminology is established. We will continue with an introduction into modern scheduling methods and briefly present how feasible schedules can be computed deploying commercial software.

Especially the computation of optimal solutions to the scheduling problem has been a popular research topic for the past decade and tremendous progress has been achieved in recent years. Therefore, we will conclude this chapter by discussing the influential contributions on this vibrant research subject.

## 2.1 Applications of Embedded Systems

Digitalisation is one of the major challenges for a modern society. As computers become increasingly dominant in every-day life the most inconspicuous objects are by now equipped with integrated computer chips. Furthermore, the growing demand of digital networking and communication, i.e. Internet of Things (IoT), will lead to increasing advances in technology and the need for small, cheap and yet reliable hardware. Already today embedded computers are by far the most common type of computer in use and experts estimate that nowadays ninety-eight per cent of all computing devices are embedded in different kinds of electronic equipment such as automotive, industrial automation, telecommunications, consumer electronics and health/medical systems [7].

However, there exists no single model for building embedded systems. This is due to many different and, partially, contradicting requirements for instance trade-offs such as resource adequacy versus best-effort strategies or predictability versus flexibility. As a consequence the system model depends strongly on the requirements of the application.

In any given application the purpose of the embedded computer system is defined by the requirements at the interface to the controlled object. Thus we will give more details on the specific requirements of architectures under investigation in the scope of this thesis: We consider *real-time* embedded systems referring to systems gathering their required information at runtime. It is commonly distinguished between two different communication protocols in multicore systems: On the one hand there is *event-triggered* communication which is dynamic and flexible and on

the other end *time-triggered* communication, whose salient features are monitoring ability and temporal predictability. The focus of this work is on the latter, the de facto standard for safety critical applications, explained in more detail in Section 2.3.

Such real-time applications are also called cyber-physical systems in order to reflect the integration of computation and physical processes. Such a distributed embedded system contains a set of node computers (nodes for short). In this work each node is considered a self-contained composite hardware/software subsystem, which communicates with each other over a time-triggered communication network.

At present, time-triggered off-chip networks such as TTP [12], FlexRay [13] and TTEthernet [14] are deployed in automotive, aerospace and railway applications. In recent years, time-triggered (TT) architectures [KB01] have gained momentum for platform-based applications. Time-triggered system architecture, especially FlexRay and TTEthernet are widely used in embedded systems for safety-critical applications. The FlexRay communication standard for instance has gained industry-wide acceptance as the next-generation automotive networking standard. Likewise, multi-processor architectures based on time-triggered on-chip networks have been introduced for safety-critical systems (e.g., GENESYS MPSoC [15], AEthereal [16]).

In the next section we will outline a novel design paradigm how these systems are actually realized in practice meeting the increasing demands of complexity, functionality and efficiency. We will then continue and discuss how the proposed architectural properties can be exploited to compute optimal schedules on the device itself.

## 2.2 SoC, NoC and MPSoC Architectures

The increasing complexity of multicore systems, together with the unending demand for higher performance and less energy consumption, keeps pushing the trend of shrinking device sizes and increasing the number of endsystems integrated on a single chip. Moore's famous law does not only describe the increasing density of transistors permitted by technological advances. It also imposes new requirements and challenges. System complexity increases at the same speed. Nowadays systems could never be designed using the same approaches applied 30 years ago [17]. New architectures are and must be continuously conceived. Hence Multiprocessor systems-on-chips (MPSoCs) are the latest incarnation of very large-scale integration (VLSI) technology. A single integrated circuit can contain over 100 million transistors, and the International Technology Roadmap for Semiconductors predicts that chips with a billion transistors are within reach [18].

In order to comply to the needs outlined designers are forced to move beyond logic design into computer architecture. The demands placed on these chips by applications require designers to face problems not confronted by traditional computer architecture: harsh operational conditions, very low-power operation and as in the scope of this work real-time deadlines. These opportunities and challenges make MPSoC design an important field of research especially regarding communication paradigms on these architectures.

In order to define MPSoC we first have to define a system-on-chip (SoC). A SoC is an integrated circuit that implements most of the functions of a complete electronic system. The most fundamental characteristic of a SoC is complexity. A memory chip may have many transistors, but its regular structure makes it a component and not a system. Exactly what components are assembled on the SoC varies with the application. It is predicted that future embedded SoCs will probably be made up of tens or hundreds of heterogeneous endsystems, which will be able to execute one parallel application or even several applications running in parallel [19].

SoCs first came up in the mid-nineties. One of the main challenges then was the way to interconnect all these devices efficiently as due to the increasing complexity the bus interconnect structure soon reached its limits and was no longer appropriate to meet the challenges of modern design patterns. Therefore a new interconnection paradigm emerged, the so-called Network-on-Chip (NoC). Basically a NoC can be described as a communication subsystem on an integrated circuit in a SoC. Therefore NoC architectures can be regarded as the solution for the scalability problem of SoCs.

SoCs can be found in many product categories ranging from every day consumer devices to industrial systems:

- Cell phones use several programmable processors to handle the signal processing and protocol tasks required by telephony. These architectures must be designed to operate at the very low-power levels provided by batteries.

- Telecommunications and networking use specialized SoCs, such as network processors, to handle the huge data rates presented by modern transmission equipment.

- Digital televisions and set-top boxes use sophisticated multiprocessors to perform real-time video and audio decoding and user interface functions.

- Television production equipment uses systems-on-chips to encode videos.

Now we can define an MPSoC as a system-on-chip containing multiple processors (CPUs). In practice, most SoCs are MPSoCs because it is too difficult to design

a complex system-on-chip without making use of multiple CPUs. In MPSoC we can in general distinguish between two communication protocols i.e. an event-triggered communication protocol where messages are triggered by an external event opposed to a time-triggered communication protocol. This thesis will focus on the latter. Details are provided in Section 2.3.

Considering architectures equipped with TT communication protocols offers several advantages i.e. monitoring aspects or the capability of providing fault tolerance: A faulty endsystem for example cannot affect the message exchange between other endsystems if the execution of jobs is scheduled to different parts of the on-chip-network still operating free from defects. On-chip fault isolation is a prerequisite for fault-tolerance through active redundancy [20] and the integration of mixed-criticality applications on a single chip [21]. This concepts and subsequent applications of our proposed framework will be introduced extensively in Chapter 7.2.

Just like SoCs MPSoCs have been used to realize a a wide range of new products and services in many areas. Their popularity arises from the average high performance. MPSoC design has been regarded an emerging research area for the last few years [22] and subsequently tremendous research is being conducted on MPSoCs. Areas of special interest regard critical issues like computational capabilities, programmability, flexibility, scalability and power consumption. Using parallel programming techniques, more efficient computational capabilities can be achieved. Such parallel task execution models have been studied for parallel computing machines during the past decades.

There are numerous examples where MPSoCs are already applied in practice especially in cost-sensitive, real-time systems: Consider for example cellular phone, game stations or high-definition digital television (HDTV). Due to the application scenarios designers face real-time performance requirements as well as stringent cost requirements (chip area, energy consumption). To satisfy those requirements, applications executed on MPSoCs need to be optimized in terms of code size, energy consumption and execution time. In this thesis we will focus on the latter and introduce a scheduling framework not only tailored to meet the requirements of MPSoC architectures described but are also executable on the target architecture itself thus meeting the requirements for software designers outlined [23].

In conclusion it can be said that MPSoC is an emerging research area and deservedly in the focus of industry and academia. As there is a huge variety of different approaches we have confined for the scope of this work that all processors of the MPSoC are assumed to be homogeneous. We will emphasize our work on scalability of scheduling within the architecture under consideration. We will inves-

tigate how the optimal scheduling problem on MPSoCs can be solved efficiently deploying parallel computation. In this context we examine how the multicore structure can be exploited for parallel execution.

## 2.3 Time-Triggered Communication Protocol

For distributed embedded systems there currently exist two fundamentally different paradigms for the design of real-time systems: In an event triggered system a processing activity is initiated as a consequence of internal or external stimuli such as the reception of a message or a rise of temperature. On the other hand a time-triggered communication protocol strictly controls the entire communication within a network determining exactly at which point in time a message is sent and received. This thesis will focus on the latter paradigm because time-triggered networks [12, 13, 14] play an important role in safety-critical systems, where their inherent properties such as temporal predictability, fault tolerance and composability [6] improve safety and reduce certification costs [7]. Time-triggered networks use timeplans, which define the points in time of all message exchanges with respect to a global time base. In multi-cluster time-triggered systems of large embedded systems (e.g., automotive, avionics), conflict-free paths along switches and endsystems are defined for each message. The conflict-free temporal and spatial allocation of communication resources in combination with an intelligent communication network (e.g., local and central guardians) prevents interference between messages from different components upon integration and in the presence of faults.

For the time-triggered communication network different topologies can be distinguished such as bus, star and ring topologies. Independently of the topology, different redundancy degrees of the communication network are possible. A single communication channel is typically used in non safety-critical applications. In *safety critical systems*, redundant communication channels support the masking of channel failures. For example, the computational components can be allocated to the nodes of a distributed system, where the network serves as the communication infrastructure between these components. Another possibility, which has been enabled by the advances of Multi-Processor System-on-a-Chips (MPSoCs), is the allocation of computational components to endsystems that are interconnected switches [17] which will be discussed in more detail in the next chapter.

Time-triggered, safety critical, distributed systems, the scope of this work, have established themselves as a de facto standard for numerous applications i.e. chassis control systems and power train communication. Therefore it seem sensible to analyse the impact of optimal schedules on the performance of the systems under

investigation.

## 2.4 Scheduling in Time-Triggered Distributed Systems

Scheduling is the act of creating a schedule, which is a timetable for planned occurrences. Scheduling may also involve allocating resources to activities over time. A scheduling problem can be viewed as a constraint satisfaction problem or as a constrained optimization problem [24], but regardless of how it is viewed, a scheduling problem is defined by:

- 1. A set of time intervals, i.e. definitions of activities, operations or tasks to be completed.

- 2. A set of temporal constraints, i.e. definitions of possible relationships between the start and end times of the intervals.

- 3. A set of specialized constraints i.e. definitions of the complex relationships on a set of intervals due to the state and finite capacity of resources.

In the state-of-the-art scheduling techniques for time-triggered networks have been introduced with different optimal techniques and heuristics. However, the scalability of optimal techniques is limited with the number of endsystems, switches and messages. Even in case of sufficient resources, heuristics cannot guarantee the computation of a feasible schedule. Thus scheduling is important but  $\mathcal{NP}$ -complete. Therefore scheduling has been a very important research subject for the past thirty years. Only recently a very attractive alternative to simulation and testing has emerged [25]: The application of formal verification tools to the scheduling problem. While simulation and testing explore only some of the possible behaviours and scenarios, formal verification conducts an exhaustive exploration of all possibilities and thus guarantees that an optimal solution is found, if it actually exists.

In this thesis, we deploy tools from the area of formal verification, such as SAT and SMT solvers, by which a desired behavioural property of a defined system model is analysed. Therefore we will develop a time-discrete model representing the tasks the on-chip-system under investigation has to perform. We consider logical dependencies as well as architectural properties, which are both outlined in Chapter 4.

One of the main objectives of this work is the application of our proposed scheduling framework on real-time systems. A real-time system must produce the intended results at the intended instant in real time [26]. Time-triggered real-time systems

are popular in safety-critical applications where temporal predictability is an important concern. In order to describe the tasks which have to be performed on the system under consideration, we use the term jobs to denote a logical unit of computation and we represent a program as a set of jobs. In literature, terms as jobs, task and processes. are used interchangeably. In many traditional real-time applications, especially in the aeronautic or automotive sector, it is assumed that the set of tasks does not change at runtime. We adopt this paradigm and throughout this thesis it is our aim to schedule a set J of n jobs, i.e.

$$J=\{j_1,j_2,\cdots j_n\}.$$

The so-called **job shop scheduling problem** is an optimization problem. It attempts to find a minimal makespan, where the **makespan** denotes the total length of the schedule. Therefore the makespan depends on the allocation of jobs to endsystems and the routes of the time-triggered messages sent between them. Both allocation and paths are fully determined by the proposed scheduling framework. Details on optimization problems and their complex challenges can be gathered from Sections 3.2 and 3.3.

In the literature it is distinguished between four different scheduling classes, which we will briefly outline:

- Static scheduling: all scheduling decisions are based on fixed parameters, assigned to tasks before their activation. Static scheduling needs a priori knowledge of all task attributes. Therefore it is less flexible.

- 2. **Dynamic scheduling**: all scheduling decisions are based on dynamic parameters that might change at runtime. Dynamic scheduling can provide a better processor utilization and supports non-predicted events such as failing components, but it has a higher runtime overhead than static scheduling.

- 3. Off-line scheduling: All scheduling decisions are computed at compile time and stored in a dispatcher table which is located in a Trusted Research Manager (TRM), d device that will not become faulty by construction. At runtime no scheduler is needed, but only a dispatcher which takes the next entry from the table. Off-line scheduling is also called table-driven scheduling, which incorporates a table determining which tasks to execute at which points in time. Thus, feasibility is proven constructively. Off-line scheduling methods are capable of managing distributed applications with complex constraints (e.g. precedence or end-to-end deadlines). On the other hand, the a-priori knowledge about all system activities may be hard or impossible to obtain. Its rigidity enables deterministic behaviour, but drastically limits flexibility.

4. **On-line scheduling**: All scheduling decisions are made at runtime, meaning that the scheduler decides when a new task is released or when a task terminates its execution. Nevertheless, on-line scheduling anomalies have to be handled.

This thesis focuses on static scheduling, because the architecture and allocation of tasks to endsystems. The off-line scheduling approach is the one usually associated with time-triggered architectures. When enhancing the proposed scheduler, however, we will also consider dynamic, on-line scheduling, especially when regarding fault tolerant architectures.

Currently timeplans are computed during the design process employing high performance computers and state-of-the-art software like IBM ILOG CPLEX Optimization Studio (often informally referred to simply as CPLEX) are deployed. We will outline how CPLEX solves scheduling problems in the next section.

Cyper-physical systems are also equipped with redundant alternative schedules to react to system failures. However these errors can never be covered completely and non-predictable failures may still cause permanent errors of the system. As memory capacities on an embedded system are limited, an effective way to compute alternative schedules meeting all deadline constraints have to be developed. Especially if optimal solutions are required and state-of-the-art-solvers cannot be deployed on the architecture under consideration due to the hardware limitations outlined above the process can be very time-consuming. Otherwise if feasible solutions are sufficient, it may prove sensible to apply heuristics to the scheduling problem. This may significantly reduce runtime but may fail to find solutions meeting all deadline constraints even if they exist.

## 2.5 MILP-based Scheduling

Scheduling is known to be a tough challenge which may prove to be time-consuming, especially if the architecture under investigation relies on optimal schedules. Therefore a common way to compute possible schedules in practice is the application of high-performance computer clusters during the design process. Hence static off-line scheduling - see previous section - is mainly deployed in the state-of-the-art. In this process efficient hard- and software computes a number of valid schedules which are then copied onto the device and stored in a TRM [27]. If components fail or the system has to be reconfigured the schedules are substituted. The TRM accepts proposals for new communication schedules, which are provided by the components. The TRM checks the validity of a supplied time-triggered schedule by checking whether it is free of collisions. However, as the computation of schedules

is not dynamic there is a high probability that the entire system may fail if the schedules stored in the TRM are not capable to mask the fault reported.

The main software adopted in the research area of embedded systems to compute schedules is IBM ILOG CPLEX Optimization Studio. CPLEX Studio is a rapid development system for optimization models with interfaces to embed models into standalone applications. We will briefly refer to this software as CPLEX deploy the version released in 2014 [28].

CPLEX is an optimization software package based originally on the Simplex algorithm. Today it solves integer programming problems using the simplex method or the barrier interior point method, convex and non-convex quadratic programming problems and convex quadratically constrained problems. CPLEX is referred to be the leading software product in the field of mathematical optimization and operational research. This work mainly relies on CPLEX as a reference solver which is on the one hand deployed to validate our results. On the other hand we compare the memory footprint as well as the computation time of our proposed scheduling framework to CPLEX. In contrast to CPLEX all other tools proposed in the course of this work are open source and free of charge.

#### 2.6 Related Work

Time-triggered networks play an important role in safety-critical systems, where their inherent properties such as temporal predictability, fault tolerance and composability [6] improve safety and reduce certification costs [7]. Time-triggered networks use timeplans, which define the points in time of all message exchanges with respect to a global time base. In multi-cluster time-triggered systems of large embedded systems (e.g., automotive, avionics), conflict-free paths along switches and endsystems are defined for each message. The conflict-free temporal and spatial allocation of communication resources in combination with an intelligent communication network (e.g., local and central guardians) prevents interference between messages from different components upon integration and in the presence of faults.

However, the computation of the timeplans is time consuming and computationally complex [8]. Feasible schedules need to avoid conflicts of communication resources, meet deadlines, satisfy precedence constraints and ensure implicit synchronization [9]. Different optimal and heuristic scheduling algorithms have been devised in the state-of-the art (e.g., enumerative methods, mathematical programming, simulated annealing, genetic algorithms, tabu search, neural networks). While the runtime of optimal algorithms becomes prohibitive upon large problem sizes, heuristics often fail to find feasible schedules.

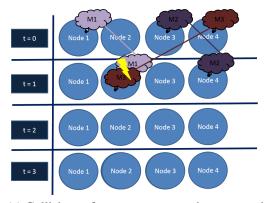

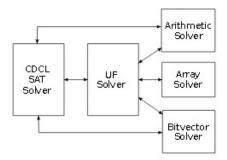

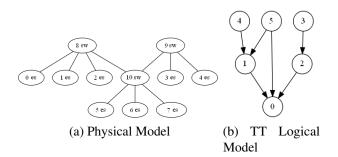

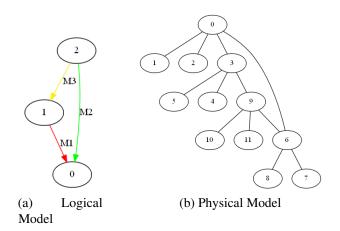

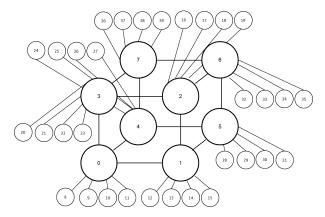

Figure 1: Logical Application Model (left) mapped to Physical Multicore Platform (right)

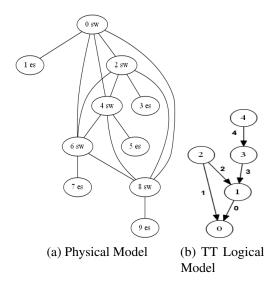

For the past five years the application of tools from hard- and software verification to the scheduling problem has been studied extensively [25]. Especially so-called SAT solvers have been applied. Modern SAT solvers use heuristics to efficiently compute solutions for the Boolean Satisfiability Problem, one of most-researched NP-complete problem in computer science [29] - see also Section 3.3. SAT solvers have demonstrated to be effective in solving  $\mathcal{NP}$ -complete problems for many applications, including planning, circuit design and also scheduling [30]. This widespread adoption is the result of the efficiency gains made during the last decade [31]. Modern SAT-solvers use different heuristics to check whether a given Boolean formula  $F(x_1, \dots, x_n)$  is satisfiable and if so returns a satisfying assignment that makes F true.

SMT solvers, which extend SAT with richer theories, can handle an even broader range of problems [32] by allowing the input of (in)-equalities expressed in classical first-order logic. SMT solvers have proved to be powerful and expressive backend engines for formal verification in many contexts, including the verification of software, hardware, and of timed and hybrid systems [33] and have been successfully used to compute feasible schedules for time-triggered networks [25]. Because of the high computation time required by existing schedulers, a technique that applies an SMT-solver to compute an optimal solution to a scheduling problem with time-triggered messages is proposed. It has been previously investigated how the scheduling problem can be translated into a conjunctive normal form (CNF) allowing the application of a SAT-solver to compute satisfiable solutions that were optimal with respect to the total transmission time to receive all messages [2].

2.6 Related Work 15

This model was however limited by the constant allocation of jobs to nodes. In this work the model is enhanced such that an arbitrary allocation of jobs to endsystems is allowed. The proposed scheduler is optimizing the allocation of jobs as well as the message paths with respect to the minimal transmission times. Furthermore the proposed SMT scheduler is able to handle multiple messages from the same sender which represents a more realistic behaviour.

In the past SMT solvers have been successfully applied to verify the TT-Ethernet synchronisation function [25]. Furthermore SMT solvers were also applicable for the generation of (even large-scale) time-triggered schedules [34]. This scheduling model proposed in [34] has also recently been evaluated using the SMT solver YICES2 [35].

Due to its multicore heritage MPSoC can also be deployed for parallel computing [36] and high performance parallel-programming frameworks for MPSoC architectures such as [37] have recently been developed. Hence we will also study the impact of parallelization of the proposed scheduling framework considering different approaches for the computation of optimal and feasible schedules. We have already previously investigated the parallel distribution of different problem instances (i.e. SAT benchmarks) to different endsystems [1]. Therefore distributing the scheduling problem and approaches to solve the partitions in parallel is also analysed in the scope of this work.

For years parallel computing has been a popular research subject. Since the switch to multicore and manycore processors industry has laid out a roadmap for multicore designs [38]. Also the use of SAT solvers [39, 40] in various application areas is on the rise since in addition to the traditional hardware and software verification domains, SAT solvers are gaining popularity in new domains. This widespread adoption is the result of the efficiency gains made during the last decade [41]. Tremendous efforts have been taken to combine the two disciplines and to apply the concept of parallelisation to improve performance of SAT solvers even further [42].

In addition to this industrial partners have defined key challenges in parallel SAT solving [41], which shows how important efficient SAT solving methods are for real-world applications.

# 3 Concepts and Terms

This chapter presents the mathematical terms and concepts used in this thesis: we explicitly introduce three basic concepts: propositional logic, mathematical optimization including the special case of pseudo-Boolean optimization problems and complexity classes for evaluation purposes.

We begin with the introduction of an algebra whose original purpose, dating back to Aristotle, was to model reasoning. In more recent times this algebra, like many other algebras, has proved useful as a design tool. We will outline the formalities and notations used to describe the Scheduling Problem using Boolean Functions and their representations only. In the same way it is demonstrated how the Scheduling Problem can be transformed into a mathematical optimization problems using so-called pseudo-Boolean variables only. Because of this we will be able to apply state-of-the-art tools from the field of computer verification to find solutions, to the Scheduling problem. In order to classify these solutions we define optimization problems. The chapter is concluded with an introduction to complexity theory which is needed to evaluate the scalability and sustainability of our proposed scheduling framework.

## 3.1 Boolean Functions and their representations

In this section we will define a Boolean algebra, introduce logical expressions with Boolean-valued operands and logical operators such as AND, OR and NOT operating on Boolean values. The sequential arrangement is inspired by [43].

A Boolean value is one with two choices: true or false, yes or no, 1 or 0. In computer science the Boolean data type is a data type, having two values intended to represent the truth values of logic in an algebra. This algebra is often called Boolean algebra after George Boole, the logician who first defined the underlying concept formally. In mathematical logic, a *propositional variable* (also called a sentential variable or sentential letter) is a variable which can either be true or false. Propositional variables are the basic building-blocks of propositional formulae, used in propositional and higher order logics.

Propositional logic is a mathematical model that allows us to reason about the truth or falsehood of logical expressions. This can be formalized by defining logical expressions as follows:

**Definition 3.1.** Propositional variables and the logical constants, TRUE and FALSE, are **logical expressions**. These are the so-called atomic operands.

**Remark 3.2.** Let E and F be logical expression. Then so are:

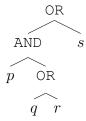

Figure 2: Expression tree for the logical expression p AND  $(q \ OR \ r)$  OR s

- E AND F. The value of this expression is TRUE if and only if both E and F are TRUE. It is FALSE, otherwise.

- E OR F. The value of this expression is TRUE if either E or F or both are TRUE. It is FALSE, if both E and F are FALSE.

- $\overline{E}$ . The value of this expression is TRUE if E is FALSE, and vice versa.

Thus logical expressions can be built from the binary infix operators AND and OR as well as the unary prefix operator NOT.

When all of the propositional variables in a logical expression are assigned truth values, the expression itself acquires a truth value. We can evaluate a logical expression just as we would with arithmetic or a relational expression. A good way to visualize this fact is the deployment of so-called *expression trees* as depicted in Figure 2. For a given truth assignment of each variable the tree is worked up from the bottom producing truth values for each node. The truth value at the root is then the truth value of the expression as a whole.

Formally a logical expression can be described as a function from the values of its arguments to a value of the whole expression. To be more precise a logical expression's meaning is a function that takes truth assignments as arguments and returns either TRUE or FALSE. Such functions are called Boolean functions and defined below. Like arithmetic expressions, Boolean expressions can be thought of as sets of pairs. The first component of each pair is a truth assignment, that is a tuple giving the truth value of each propositional variable in some specified order. The second component of the pair is the value of the expression for that truth assignment.

Before we can explicitly define Boolean functions we have to introduce Boolean domains:

**Definition 3.3.** A Boolean domain is a set consisting of exactly two elements usually written as  $\{0,1\}$  or  $\{TRUE, FALSE\}$ .

Throughout this work we will denote Boolean domains as  $\mathbb{B}$ . Hence Boolean functions can be defined as follows:

#### **Definition 3.4.** A Boolean function is a function of the form

$$f: \mathbb{B}^k \longrightarrow \mathbb{B},$$

where  $\mathbb{B}$  is a Boolean domain. The non-negative integer k is called the **arity** of the Boolean function. If k = 0 the Boolean function f is constant which means it always evaluates to the same element of  $\mathbb{B}$ .

In Boolean functions we will use the following symbols to denote infix operators:  $\vee$  for  $\bigcirc R$  and  $\wedge$  for  $\bigcirc R$  and  $\cap$  for  $\bigcirc$  for  $\bigcirc$

$$f: \mathbb{B}^4 \longrightarrow \mathbb{B}: (p, q, r, s) \in \mathbb{B}^4 \mapsto p \vee (q \wedge r) \vee s.$$

It is convenient to display a Boolean function as a *truth table*, in which the rows correspond to all possible combinations of truth values for the arguments. There is a column for each argument and a column for the value of the function. Our introductory example is evaluated in the truth table depicted in Table 1.

The example illustrates that four variables require  $2^4 = 16$  assignments in order to fully evaluate all possibilities. This conjunction holds and in fact the truth table for Boolean function of arity k consists of  $2^k$  row, one for each truth assignment. Therefore it is highly complex to compare two Boolean functions as well as to fully evaluate Boolean functions or to prove that no valid truth assignment exits for a given Boolean function. We will discuss the complexity of this problem in more detail in Section 3.3.

The importance of Boolean algebras for computer science goes back to 1938, when it was proven that a two-valued Boolean algebra can describe the operation of two-valued electrical switching circuits [44]. Table 2 depicts the truth table for the  $2^{2^2} = 16$  possible Boolean functions of two binary variables of the form:

$$f: \mathbb{B}^2 \longrightarrow \mathbb{B}, \ (p,q) \in \mathbb{B}^2 \mapsto f(p,q).$$

In addition to the two Boolean functions we have already met, hence AND i.e.  $F_7$  and OR i.e.  $F_1$ , we want to draw attention to five additional Boolean functions of two arguments, which will prove useful in the context of this thesis:

| p | q | r | s | $q \vee r$ | $p \wedge (q \vee r)$ | $p \land (q \lor r) \lor s$ |

|---|---|---|---|------------|-----------------------|-----------------------------|

| 1 | 1 | 1 | 1 | 1          | 1                     | 1                           |

| 1 | 1 | 1 | 0 | 1          | 1                     | 1                           |

| 1 | 1 | 0 | 1 | 1          | 1                     | 1                           |

| 1 | 1 | 0 | 0 | 1          | 1                     | 1                           |

| 1 | 0 | 1 | 1 | 1          | 1                     | 1                           |

| 1 | 0 | 1 | 0 | 1          | 1                     | 1                           |

| 1 | 0 | 0 | 1 | 0          | 0                     | 1                           |

| 1 | 0 | 0 | 0 | 0          | 0                     | 0                           |

| 0 | 1 | 1 | 1 | 1          | 0                     | 1                           |

| 0 | 1 | 1 | 0 | 1          | 0                     | 0                           |

| 0 | 1 | 0 | 1 | 1          | 0                     | 1                           |

| 0 | 1 | 0 | 0 | 1          | 0                     | 0                           |

| 0 | 0 | 1 | 1 | 1          | 0                     | 1                           |

| 0 | 0 | 1 | 0 | 1          | 0                     | 0                           |

| 0 | 0 | 0 | 1 | 0          | 0                     | 1                           |

| 0 | 0 | 0 | 0 | 0          | 0                     | 0                           |

Table 1: Truth Table for for the logical expression  $p \wedge (q \vee r) \vee s$

| p | q | $F_0$ | $F_1$ | $F_2$ | $F_3$ | $F_4$ | $F_5$ | $F_6$ | $F_7$ |

|---|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 1 | 1 | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| 1 | 0 | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     |

| 0 | 1 | 1     | 1     | 0     | 0     | 1     | 1     | 0     | 0     |

| 0 | 0 | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     |

| p | q | $F_8$ | $F_9$ | $F_{10}$ | $F_{11}$ | $F_{12}$ | $F_{13}$ | $F_{14}$ | $F_{15}$ |

|---|---|-------|-------|----------|----------|----------|----------|----------|----------|

| 1 | 1 | 0     | 0     | 0        | 0        | 0        | 0        | 0        | 0        |

| 1 | 0 | 1     | 1     | 1        | 1        | 0        | 0        | 0        | 0        |

| 0 | 1 | 1     | 1     | 0        | 0        | 1        | 1        | 0        | 0        |

| 0 | 0 | 1     | 0     | 1        | 0        | 1        | 0        | 1        | 0        |

Table 2: Truth Table for all possible Boolean functions  $F_i, i \in \{0, 1, \dots 15\}$  of two binary variables

- $F_4$ , denoted with Boolean expression  $\overline{p} \vee q$  also referred to as *Implication* in propositional logic, denoted with  $\Longrightarrow$ . The respective truth table is also depicted in Table 3a.

- $F_6$ , denoted with Boolean expression  $(p \land q) \lor (\overline{p} \land \overline{q})$  also referred to as *Equivalence* in propositional logic, denoted with  $\Leftrightarrow$  or XNOR in digital logic. The respective truth table is also depicted in Table 3b.

- $F_8$  denoted with Boolean expression  $\overline{p \wedge q}$  also referred to as NAND-operator. The respective truth table is also depicted in Table 3c.

- $F_9$  denoted with the Boolean expression  $(p \wedge \overline{q}) \vee (\overline{p} \wedge q)$  also expressed as **Exclusive or**, denoted  $\oplus$  in digital logic. The respective truth table is depicted in Table 3d.

|     |         |                                                  |                |         |                         |                |                          |                           |                       | _      |                  |                          |          |                            |

|-----|---------|--------------------------------------------------|----------------|---------|-------------------------|----------------|--------------------------|---------------------------|-----------------------|--------|------------------|--------------------------|----------|----------------------------|

| p   | q       | $\overline{p} \vee \overline{q}$                 | q              |         | p                       | q              | $p \wedge q$             | $(p) \vee (\overline{p})$ | $\wedge \overline{q}$ |        |                  | p                        | q        | $\overline{p \wedge q}$    |

| 1   | 1       | 1                                                |                |         | 1                       | 1              |                          | 1                         |                       |        |                  | 1                        | 1        | 0                          |

| 1   | 0       | 0                                                |                |         | 1                       | 0              |                          | 0                         |                       | 7      |                  | 1                        | 0        | 0                          |

| 0   | 1       | 1                                                |                |         | 0                       | 1              |                          | 0                         |                       |        |                  | 0                        | 1        | 0                          |

| 0   | 0       | 1                                                |                |         | 0                       | 0              |                          | 1                         |                       | 7      |                  | 0                        | 0        | 1                          |

| (a) | $F_4$ i | $\overline{.e.\overline{p}} \vee \overline{.e.}$ | $\overline{q}$ |         | (b                      | $F_6$          | i.e. $(p \land$          | $q) \vee (\overline{p}$   | $\wedge \overline{q}$ |        |                  | (c)                      | $F_8$ i. | e. $\overline{p \wedge q}$ |

|     |         |                                                  |                |         |                         |                |                          |                           |                       |        |                  |                          |          |                            |

|     |         | p                                                | q              | (p)     | $\wedge \overline{q})$  | V (            | $\overline{p} \wedge q)$ |                           | p                     | q      | $\overline{(p)}$ | $\vee q$                 | <u>)</u> |                            |

|     |         | 1                                                | 1              |         |                         | 0              |                          |                           | 1                     | 1      |                  | 0                        |          |                            |

|     | 1 0     |                                                  |                | 1       |                         |                |                          | 1                         | 0                     |        | 1                |                          |          |                            |

|     |         | 0                                                | 1              |         | 1                       |                |                          | 0                         | 1                     |        | 1                |                          |          |                            |

|     |         | 0                                                | 0              |         |                         | 0              |                          |                           | 0                     | 0      |                  | 1                        |          |                            |

|     |         | (d                                               | $F_9$          | i.e. (1 | $p \wedge \overline{q}$ | <u>(</u> ) ∨ ( | •                        | (e)                       | $F_{14}$ i            | i.e. ( | $p \vee e$       | $\frac{\overline{q}}{q}$ |          |                            |

Table 3: Truth Tables for Additional Logical Operators.

The representation of a Boolean function is not unique. In fact it can be represented by an infinite number of Boolean formulae. Consider for example the simple Boolean function  $f = p \land q$ , which is the same as

$$f = q \land p = (p \land q) \land (p \land q) = \cdots$$

A truth table is the simplest way of representing a Boolean function and starting from here any Boolean function whatsoever can be represented by a logical expression using the operators AND, OR, and NOT. Finding the simplest expression for a given Boolean function is generally hard. However, we can easily construct some expression for any Boolean function. Starting with the truth table for the function, we construct a logical expression of the form

$$m_1 \vee m_2 \vee \cdots \vee m_n$$

.

Each  $m_i$  is a term that corresponds to one of the rows in the truth table evaluating to 1. The terms  $m_i$  are of special form and have to obey certain rules, which we want to outline in the following:

A **literal** is a Boolean expression that is either a single propositional variable, such as p, or negated variable NOT p, which we will in future denote  $\overline{p}$ . Consider a truth table consisting of k variables then each  $m_i$  is the composition of k literals. If in row i the variable p is of value 1 select the literal p otherwise choose  $\overline{p}$ . If we continue in this fashion  $m_i$  is the logical conjunction of the literals. Clearly

$m_i$  can only evaluate to TRUE if all variables have the values that appear in the corresponding row of the truth table.

**Definition 3.5.** If  $m_i$  is constructed in the way described  $m_i$  will is called **minterm**. If all minterms are combined using the operator OR the resulting expression

$$m_1 \vee m_2 \vee \cdots \vee m_n$$

is called the disjunctive normal form (DNF).

The expression describes the Boolean function under consideration, because it has the value 1 exactly when there is a minterm with value 1. A minterm cannot be 1 unless the values of the variables correspond to the row of the truth table for that minterm. Thus the representation is correct.

In a dual way we can also construct a representation by defining a **maxterm**, which is the disjunction of those literals disagreeing with the value of one of the argument variables in that row. More precisely this means: if the row has value 0 for variable p, select the literal p and if the value of that row for p is 1, choose  $\overline{p}$ . If the maxterms are combined conjunctively the expression is described in so-called **conjunctive normal form (CNF)**.

We can summarize the above as follows: A Boolean function f can be represented using its minterms and maxterms. This disjunction of all minterms, where f is mapped to 1 results in a DNF. Similarly, the conjunction of all maxterms, where f evaluates to 0, results in a CNF.

As an example consider again

$$f: \mathbb{B}^4 \longrightarrow \mathbb{B}: (p, q, r, s) \in \mathbb{B}^4 \mapsto p \vee (q \wedge r) \vee s.$$

whose truth table has been illustrated in Table 1. We extend this truth table by adding an extra column to describe the corresponding minterms and maxterms. The result is depicted in Table 4. Hence we can now formulate the two normal forms:

1. DNF:

$$f = m_1 \vee m_2 \vee m_3 \vee m_4 \vee m_5 \vee m_7 \vee m_9 \vee m_{11} \vee m_{13} \vee m_{15}$$

.

2. CNF:

$$f = m_8 \wedge m_{10} \wedge m_{12} \wedge m_{14} \wedge m_{16}$$

.

In the same way we can also formulate normal forms for the Boolean functions explicitly introduced in Table 3:

•  $F_4$ :

1. DNF:

$$(p \wedge q) \vee (\overline{p} \wedge q) \vee (\overline{p} \wedge \overline{q})$$

.

```

2. CNF: (\overline{p} \vee q).

```

$\bullet$   $F_6$ :

1. DNF:  $(p \wedge q) \vee (\overline{p} \wedge \overline{q})$ .

2. CNF:  $(\overline{p} \lor q) \land (p \lor \overline{q})$

• F<sub>8</sub>:

1. DNF:  $(\overline{p} \wedge \overline{q})$ .

2. CNF:  $(\overline{p} \lor q) \land (p \lor \overline{q}) \land (\overline{p} \lor \overline{q})$

$\bullet$   $F_9$ :

1. DNF:  $(p \wedge q) \vee (\overline{p} \wedge \overline{q})$ .

2. CNF:  $(\overline{p} \vee \overline{q}) \wedge (p \vee q)$

•  $F_{14}$ :

1. DNF:  $(p \wedge \overline{q}) \vee (\overline{p} \wedge q) \vee (\overline{p} \wedge \overline{q})$ .

2. CNF:  $(\overline{p} \vee \overline{q})$

We are now in the position to find a representation in CNF or DNF for every Boolean function. Throughout this work we will restrict our attention to CNFs. Finding assignments to the variables of a Boolean formula expressed in CNF is a very prominent research subject. These problems are called **Boolean Satisfiability Problems** or **SAT**-problems. They ask whether for a given Boolean formula there exits an assignment for all variables involved such that the whole expression evaluates to TRUE. In other words, the SAT-problem asks whether the variables of a given Boolean formula can be consistently replaced by the values TRUE or FALSE in such a way that the formula evaluates to TRUE. If such an assignment exists the formula is called **satisfiable** or **sat**. On the other hand, if no such assignment exists, the function expressed by the formula is FALSE for all possible variable assignments and the formula is thus **unsatisfiable** or **unsat**. This decision problem is of central importance in various areas of computer science, including theoretical computer science, complexity theory, algorithmics, cryptography and artificial intelligence.

In the following chapters we will propose the application of modern SAT solvers to the scheduling problem. SAT solvers are very powerful tools from the field of Electronic Design Automation and have contributed to dramatic advances in our ability to automatically solve problem instances involving tens of thousands of variables and millions of constraints (i.e. clauses). An extension that has gained significant popularity since 2003 is Satisfiability modulo theories (SMT) that can enrich CNF formulae with linear constraints, arrays, all-different constraints or uninterpreted functions.

In Chapter 4 we will apply the techniques introduced here to formulate equations modelling the scheduling problem and deploy SAT solvers to find solutions. This approach is enhanced in Chapter 5 where we will also apply SMT solvers to the scheduling problem.

| p | q | r | s | $q \vee r$ | $p \wedge (q \vee r)$ | $p \wedge (q \vee r) \vee s$ | terms                                                                    |

|---|---|---|---|------------|-----------------------|------------------------------|--------------------------------------------------------------------------|

| 1 | 1 | 1 | 1 | 1          | 1                     | 1                            | $m_1 = p \land q \land r \land s$                                        |

| 1 | 1 | 1 | 0 | 1          | 1                     | 1                            | $m_2 = p \wedge q \wedge r \wedge \overline{s}$                          |

| 1 | 1 | 0 | 1 | 1          | 1                     | 1                            | $m_3 = p \wedge q \wedge \overline{r} \wedge s$                          |

| 1 | 1 | 0 | 0 | 1          | 1                     | 1                            | $m_4 = p \wedge q \wedge \overline{r} \wedge \overline{s}$               |

| 1 | 0 | 1 | 1 | 1          | 1                     | 1                            | $m_5 = p \wedge \overline{q} \wedge r \wedge s$                          |

| 1 | 0 | 1 | 0 | 1          | 1                     | 1                            | $m_6 = p \wedge \overline{q} \wedge r \wedge \overline{s}$               |

| 1 | 0 | 0 | 1 | 0          | 0                     | 1                            | $m_7 = p \wedge \overline{q} \wedge \overline{r} \wedge s$               |

| 1 | 0 | 0 | 0 | 0          | 0                     | 0                            | $m_8 = \overline{p} \vee q \vee r \vee s$                                |

| 0 | 1 | 1 | 1 | 1          | 0                     | 1                            | $m_9 = \overline{p} \wedge q \wedge r \wedge s$                          |

| 0 | 1 | 1 | 0 | 1          | 0                     | 0                            | $\boxed{m_{10} = p \vee \overline{q} \vee \overline{r} \vee s}$          |

| 0 | 1 | 0 | 1 | 1          | 0                     | 1                            | $m_{11} = \overline{p} \wedge q \wedge \overline{r} \wedge s$            |

| 0 | 1 | 0 | 0 | 1          | 0                     | 0                            | $m_{12} = p \wedge \overline{q} \wedge r \wedge s$                       |

| 0 | 0 | 1 | 1 | 1          | 0                     | 1                            | $m_{13} = \overline{p} \wedge \overline{q} \wedge r \wedge s$            |

| 0 | 0 | 1 | 0 | 1          | 0                     | 0                            | $m_{14} = p \vee q \vee \overline{r} \vee s$                             |

| 0 | 0 | 0 | 1 | 0          | 0                     | 1                            | $m_{15} = \overline{p} \wedge \overline{q} \wedge \overline{r} \wedge s$ |

| 0 | 0 | 0 | 0 | 0          | 0                     | 0                            | $m_{16} = p \vee q \vee r \vee s$                                        |

Table 4: Truth Table for the logical expression  $p \land (q \lor r) \lor s$  including minterms and maxterms.

25

## 3.2 Optimization

This subsection presents the concept of mathematical optimization which we want to deploy in order to compute optimal communication schedules for the architectures under investigation. This introduction to optimization problems has been inspired by [45].

#### **Mathematical Optimisation**

An amazing variety of practical problems involving decision making (or system design, analysis and operation) can be cast in the form of a mathematical optimisation problem. Indeed, mathematical optimisation has become an important concept in many areas. It is widely used in engineering, in electronic design automation, automatic control systems, and optimal design problems arising in civil, chemical, mechanical, and aerospace engineering. optimisation is used for problems arising in network design and operation, finance, supply chain management, scheduling, and many other areas.